فهرست مطالب

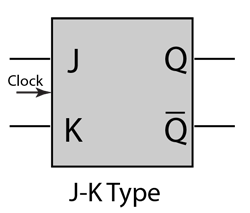

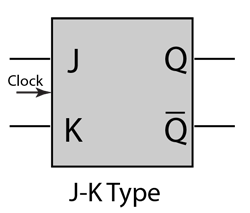

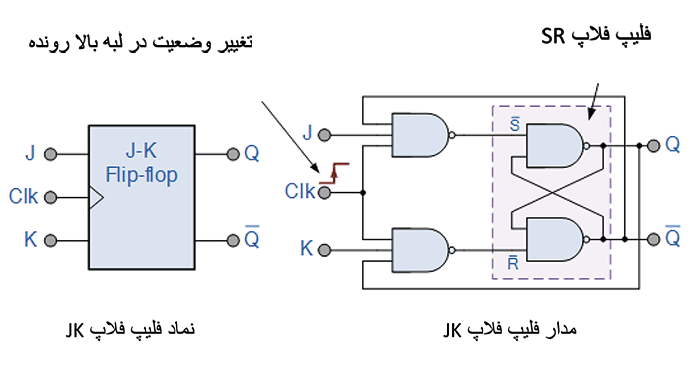

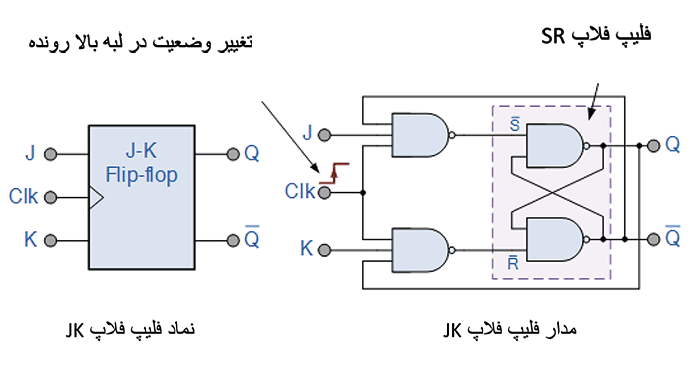

فلیپ فلاپ JK

فلیپ فلاپ JK پرکاربردترین فلیپ فلاپ است. این نوع فلیپ فلاپ یک مدار فلیپ فلاپ جهانی در نظر گرفته می شود. دارای دو ورودی است که به طور سنتی J و K برچسب گذاری شده اند. اگر J و K متفاوت باشند، خروجی Q مقدار J را در لبه ساعت بعدی می گیرد. ورودی ها به افتخار مخترع دستگاه، جک کیلبی (Jack Kilby)، برچسب های J و K دارند. برای خرید فلیپ فلاپ با قیمتی مناسب و کیفیتی عالی به فروشگاه اینترنتی دیجی قطعه مراجعه کنید.

فلیپ فلاپ JK شبیه به فلیپ فلاپ SR است، اما هیچ تغییری در حالت هنگامی که هر دو ورودی J و K پایین1 هستند وجود ندارد.

پایه مدار فلیپ فلاپ NAND S-R مزایای زیادی دارد و در مدارهای منطقی ترتیبی استفاده میشوند ( اما این فلیپ فلاپها دو مشکل اساسی دارند)

- ست2=0 و ریست3=0 شرط(S=R=0 ) هیچ وقت نباید اتفاق بیفتد.

- در زمانی که ورودی فعالساز (Enable) در حالت یک منطقی قرار دارد، اگر Set یا Reset تغییر سطح منطقی دهند، این احتمال وجود دارد که عمل نگهداری یا (Latching) اتفاق نیفتد.

سپس برای غلبه بر این دو مشکل اساسی طراحی در طراحی فلیپ فلاپ SR، فلیپ فلاپ JK گسترش یافته است.

این فلیپ فلاپ JK ساده رایج ترین فلیپ فلاپ مورد استفاده در تمام طراحی های فلیپ فلاپ موجود است و به صورت یک مدار فلیپ فلاپ (عمومی) درنظر گرفته شده است. دو ورودی نام گذاری شده با “J” و “k ” حروف مستقلی هستند و شکل اختصاری هیچ کلمهای مانند “S” برای ست و ” R ” برای ریست نیستند، که توسط مخترع آن Jack Kilby برای تمایز طراحی فلیپ فلاپ از انواع دیگر انتخاب شده اند.

(عملکرد) ترتیبی فلیپ فلاپ JK دقیقا مشابه با فلیپ فلاپ SR قبلی با همان ورودی های ” ست” و ” ریست” است (با این تفاوت که در فلیپفلاپ JK حالت ممنوعه وجود ندارد و ورودیهای J و K به صورت همزمان میتوانند یک (1) منطقی شوند)

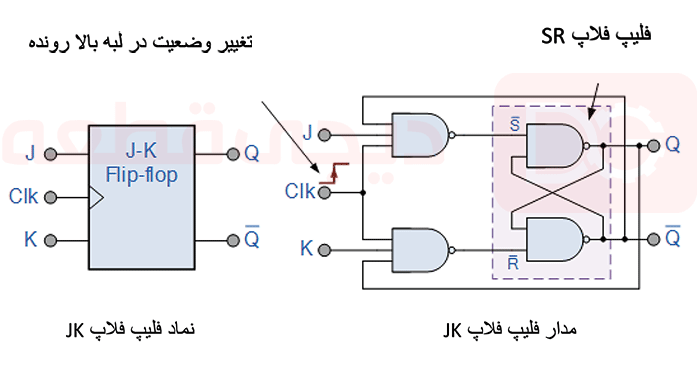

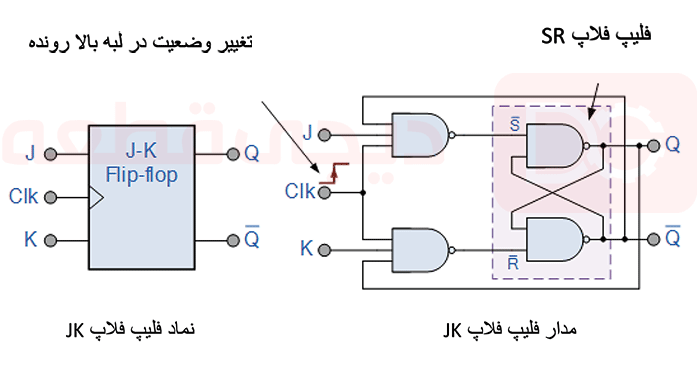

فلیپ فلاپ JK بصورت اساسی یک فلیپ فلاپ SR گیت دار به اضافه (مدار پالس ساعت) است که از رخ دادن شرایط خروجی نامعتبر یا غیرمجاز هنگامی که هر دو ورودی S و Rبرابر با سطح منطقی “1” هستند، ممانعت میکند. به دلیل این (مدار پالس ساعت)، (4 حالت ممکن برای ورودی های فلیپ فلاپ جی کی وجود دارد)، ” (سطح منطقی 1)”، ” (سطح منطقی0) “، ” بدون تغییر” و ” (حالت toggle)”. نماد این نوع فلیپ فلاپ مشابه با یک قفل SR دو وضعیتی پایدار به جز اضافه شدن یک ورودی ساعت است که در آموزش قبلی دیدیم.

اساس فلیپ فلاپ JK

تغییر وضعیت پالس ساعت در لبه بالارونده

هر دو ورودی S و R از SR دو وضعیتی پایدار قبلی اکنون با دو ورودی J و K جایگزین شده اند. بنابراین روابط برابر با: J=S و K=R است.

گیت های AND 2 ورودی دو وضعیتی پایدار SR اکنون با گیت های NAND 3 ورودی جایگزین شده اند بطوریکه ورودی سوم از هر گیت به خروجی ها در Q و [latex] bar{Q} [/latex] وصل شده اند. این پیوند متقاطع از فلیپ فلاپ SR (اجازه می دهد که حالت نامعتبر در فلیپفلاپ SR، یعنی S=1 و R=1 به عنوان وضعیت جدید Toggle مورد استفاده قرار گیرد).

اگر مدار اکنون در وضعیت “ست” باشد، ورودی J توسط وضعیت خروجی [latex] bar{Q} [/latex] “0” از طریق گیت NAND پایین تر (بی اثر) می شود. اگر مدار در وضعیت “ریست” باشد، ورودی K توسط وضعیت خروجی Q “0” از طریق گیت NAND بالاتر (بی اثر) می شود. از آنجا که Q و [latex] bar{Q} [/latex] همیشه متفاوت هستند، میتوانیم از آنها برای کنترل ورودی استفاده کنیم. هنگامی که هر دو ورودی J و K (به صورت همزمان 1 منطقی شوند)، فلیپ فلاپ JK همانطور که در جدول درستی زیر نشان داده شده است، (در وضعیت Toggle قرار میگیرد.)

جدول فلیپ فلاپ JK

درواقع فلیپ فلاپ JK اساسا یک فلیپ فلاپ SR با فیدبک است که تنها دو ترمینال ورودی آن ست یا ریست را فعال میکند تا در هر زمان فعال باشند اجازه می دهد که حالت نامعتبر در فلیپفلاپ SR، یعنی S=1 و R=1 اتفاق افتد.

همچنین هنگامی که هر دو ورودی Jو K (به طور همزمان) در سطح منطقی “1” هستند، و ورودی ساعت به “بالا” تغییر جهت یافته، مدار از حالت ست خود به یک حالت ریست و یا برعکس “toggle” خواهد شد. این نتیجه در فلیپ فلاپ SR بیشتر شبیه به یک فلیپ فلاپ نوع T معکوس هنگامی که هر دو ترمینال “بالا” هستند، عمل میکند.

اگرچه، این مدار حالت بهبودیافته فلیپ فلاپ SR است اما همچنان اگر خروجی Q حالت را قبل از اینکه پالس زمان ورودی ساعت به حالت “خاموش” برود، تغییر دهد از مسائل زمانبندی که “نرخ” نامیده میشود، رنج میبرد. برای جلوگیری از این مشکل، تناوب پالس ساعت (T) باید تا حد ممکن کوچک نگه داشته شود (فرکانس بالا). از آنجا که گاهی اوقات این با آی سی های TTL مدرن امکانپذیر نیست، فلیپ فلاپ بهبود یافته Master-Slave4 JK. توسعه یافتهاند.

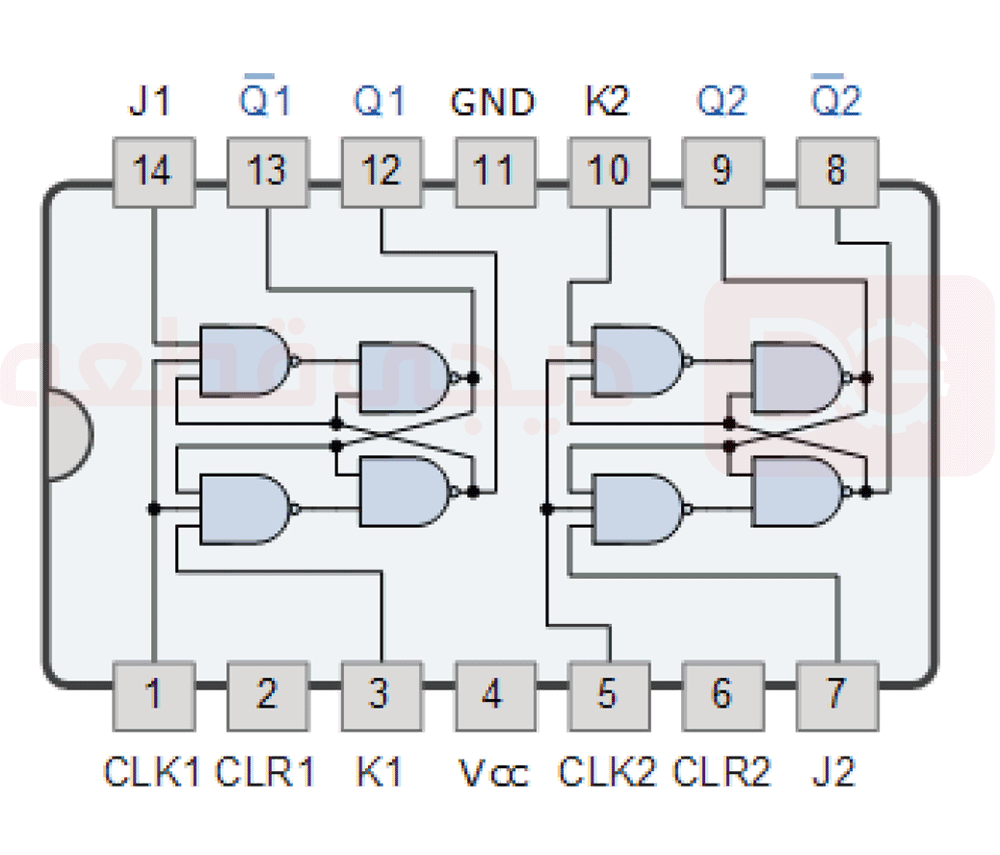

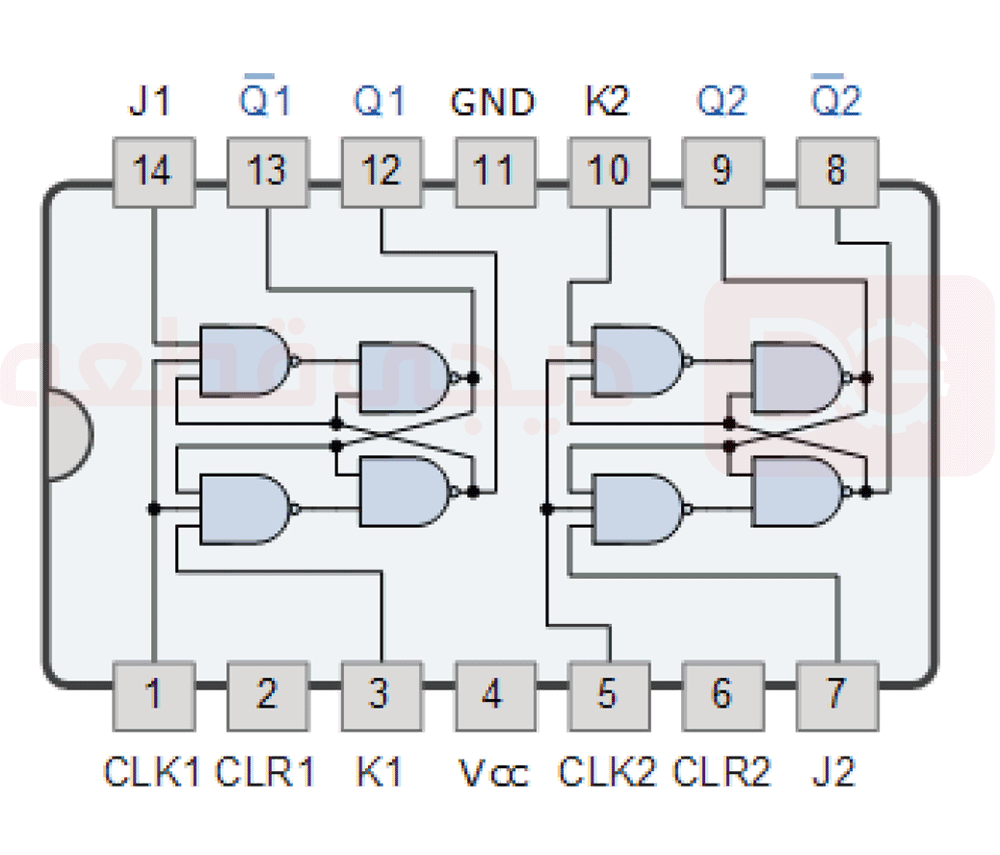

فلیپ فلاپ JK دوتایی 74LS73

آی سی های معروف فلیپ فلاپ JK

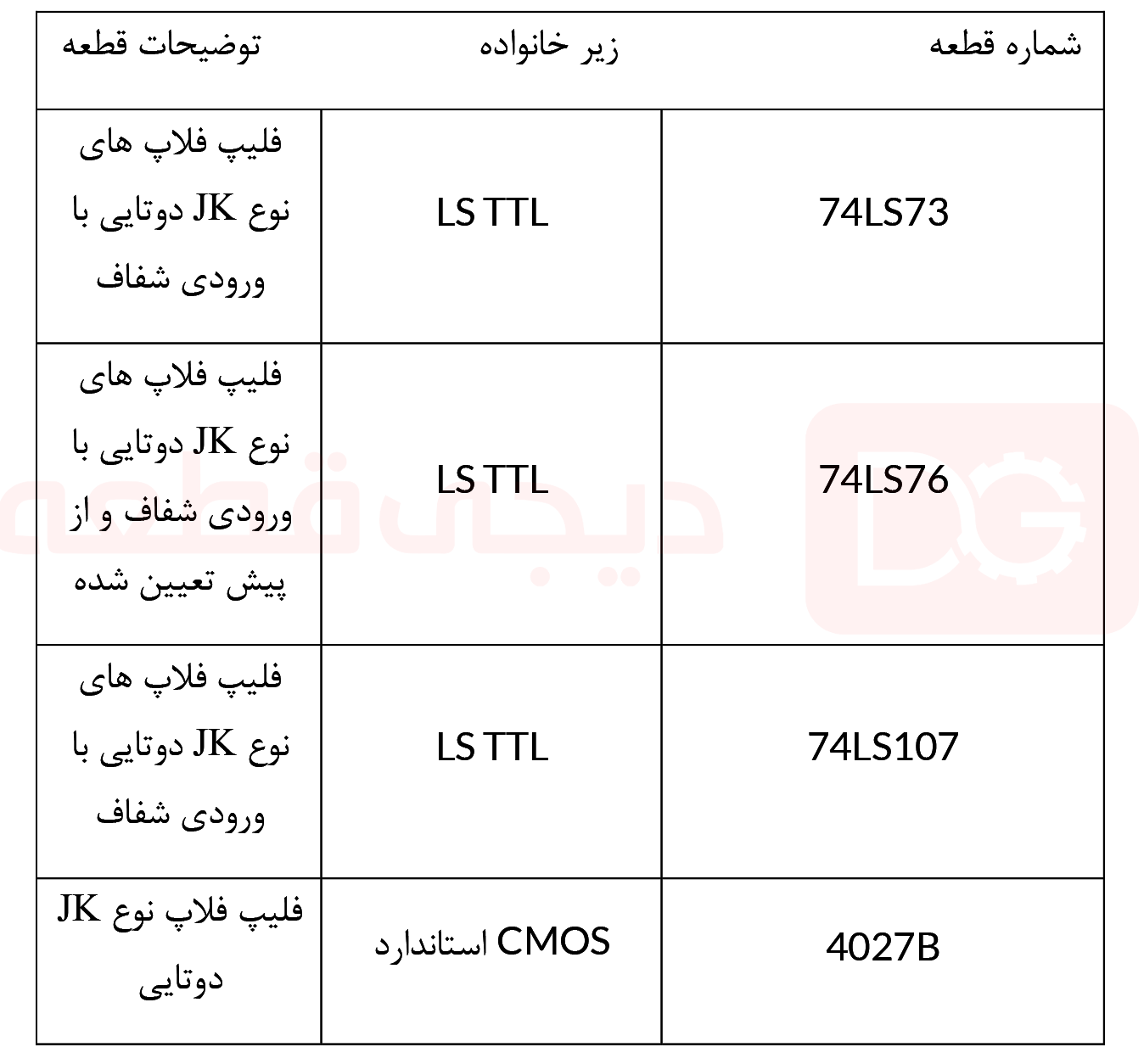

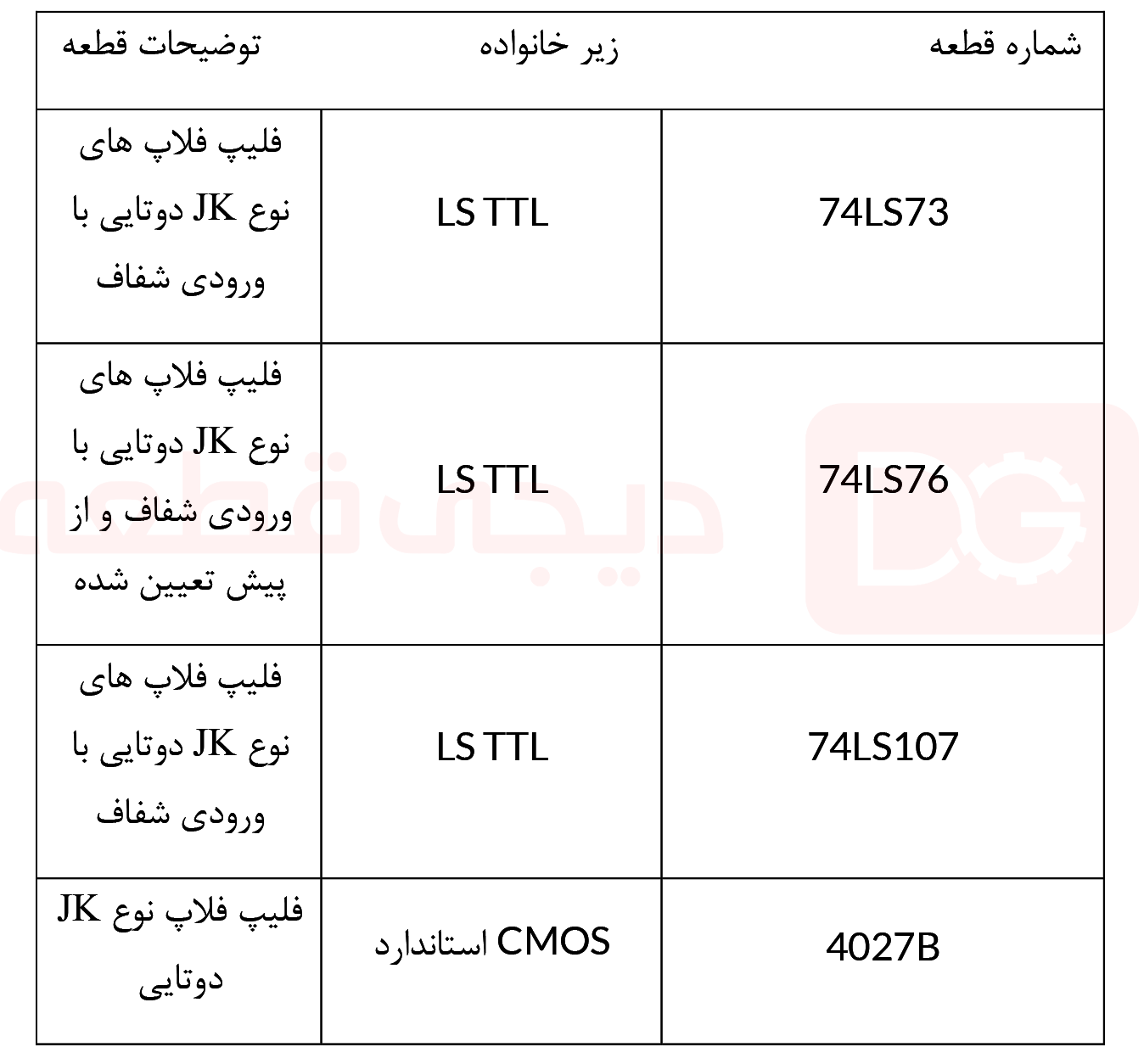

فلیپ فلاپ های JK جزو دسته آی سی های منطقی هستند. در ادامه جدولی از معروف ترین آیسی فلیپ فلاپ های JK ارائه شده است.

فلیپ فلاپ JK Master-Slave

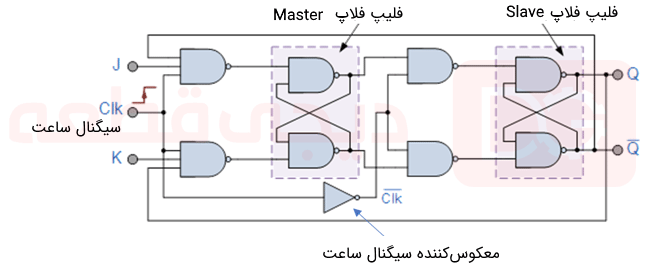

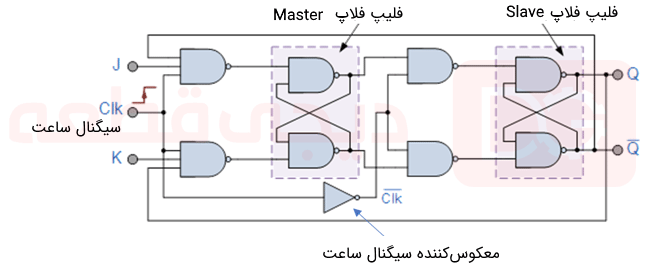

فلیپ فلاپ master-slave تمام مشکلات زمانبندی را با استفاده از دو فلیپ فلاپ SR که در یک پیکربندی سری به هم وصل شده اند، از بین می برد. یک فلیپ فلاپ به عنوان مدار “Master” عمل میکند، ( حساس به لبههای بالارونده سیگنال ساعت است) و دیگری به عنوان مدار “Slave” عمل میکند، که ( حساس به لبههای پایین رونده سیگنال ساعت است) این در دو بخش نتیجه میدهد، بخش Master و بخش Slave در طول نیم سیکل سیگنال ساعت فعال میشود.

TTL 74LS73 یک آی سی فلیپ فلاپ JK دوتایی است که شامل دو نوع دو وضعیتی پایدار JK مستقل در داخل یک تراشه واحد است که امکان ایجاد فلیپ فلاپ های master-slave یا واحد را فراهم میکند. سایر آی سی های فلیپ فلاپ جی کی شامل فلیپ فلاپ JK دوتایی 74LS107 با ورودی شفاف، فلیپ فلاپ JKتریگر شده در لبه مثبت دوتایی 74LS109 و فلیپ فلاپ تریگر شده در لبه منفی دوتایی 74LS112 با هر دو ورودی شفاف و از پیش تعیین شده است.

فلیپ فلاپ Master-Slave اساسا دو فلیپ فلاپ SR گیت دار متصل به یکدیگر در یک پیکربندی سری با Slave است که دارای پالس ساعت معکوس است. خروجی های Q و [latex] bar{Q} [/latex] از فلیپ فلاپ “Slave” به ورودی های “Master ” فیدبک شده اند با خروجی هایی از فلیپ فلاپ “Master” که به دو ورودی فلیپ فلاپ “Slave” متصل شده اند. این پیکربندی فیدبک از خروجی Slave به ورودی Master ویژگی تغییر وضعیت فلیپ فلاپ JK را همانطور که در شکل زیر نشان داده شده ارائه میکند.

سیگنالهای ورودی J و K به فلیپ فلاپ SR “Master” در حالی که ورودی پالس ساعت (CLK)”در لبه بالا رونده” و در سطح منطقی “1” است وصل شده اند. از انجا که پالس ساعت فلیپ فلاپ ” Slave” معکوس پالس ساعت ” Master” است فلیپ فلاپ SR ” Slave” (تغییر وضعیت نمی دهد (خروجی فلیپ فلاپ ” Master” به عنوان ورودی فلیپ فلاپ ” Slave”می باشد و زمانی که پالس ساعت در لبه پایین رونده یا سطح منطقی “0” باشد، در انتها خروجی” دیده ” میشوند.

هنگامی که (پالس ساعت در لبه پایین رونده یا سطح منطقی “0” باشد)، خروجی های فلیپ فلاپ ” Master” (تغییر وضعیت نمی دهد) و هر تغییر اضافه ای به ورودی های آن نادیده گرفته میشوند. فلیپ فلاپ ” Slave” گیت دار اکنون به حالت ورودی خود که توسط بخش ” Master” ایجاد شده است، پاسخ میدهد.

در گذر از “پایین به بالا” پالس ساعت، ورودی های فلیپ فلاپ ” Master” توسط ورودی های فلیپ فلاپ ” Slave” تغذیه میشوند و در گذر از “بالا به پایین”، همان ورودی ها در خروجی ” Slave” منعکس شده و این نوع از فلیپ فلاپ را به صورت تریگرشده لبه یا پالس تبدیل میکنند.

(بنابراین)، مدار هنگامی که سیگنال پالس ساعت “بالا” است، داده های ورودی را میپذیرد و داده ها را به خروجی روی لبه رو به پایین سیگنال ساعت منتقل میکند. به عبارت دیگر، فلیپ فلاپ نوع JK Master-Slave یک قطعه “همزمان” است زیرا که تنها با زمان بندی سیگنال ساعت داده را منتقل میکند.

در آموزش بعدی در مورد مدارهای منطقی ترتیبی، بر مولتی ویبراتورها که به عنوان مولد شکل موج برای تولید سیگنال های ساعت برای تغییر مدارهای ترتیبی استفاده میشوند، خواهیم پرداخت.

- LOW

- Set

- Reset

- یک طرح ارتباطی است که در آن یک دستگاه یا فرایند بر روی یک یا چند دستگاه کنترل یک طرفه دارد. در بعضی از سیستمها یک مدیر از میان یک گروه از دستگاهها برگزیده میشود و بقیه دستگاهها در نقش دستور گیر کار میکنند.

بسیار عالی و آموزنده