تقویتکننده JFET منبع مشترک از ترانزیستورهای اثر میدانی پیوندی به عنوان قطعه فعال اصلی خود استفاده میکند که مشخصات امپدانس ورودی بالا را ارائه میکند.

فهرست مطالب

JFET منبع مشترک

مدارهای تقویت کننده ترانزیستور مانند تقویت کننده امیتر مشترک با استفاده از ترانزیستورهای دوقطبی ساخته شده اند اما تقویت کننده های سیگنال کوچک همچنین میتوانند با استفاده از ترانزیستورهای اثر میدانی ساخته شوند. این قطعات دارای مزیتی نسبت به ترانزیستورهای دوقطبی هستند که آن داشتن یک امپدانس ورودی شدیدا بالا همراه با یک خروجی با نویز پایین است که آنها را برای استفاده در مدارهای تقویت کننده که دارای سیگنالهای ورودی بسیار کوچک هستند ایده آل میکند.

طراحی یک مدار تقویتکننده بر اساس یک ترانزیستور اثر میدانی پیوندی یا “JFET” ( FET N کانال برای این آموزش) یا حتی یک FET سیلیکون اکسید مثال یا “MOSFET” دقیقا مانند همان اصول که برای مدار ترانزیستور دو قطبی که برای یک مدار تقویتکننده کلاس A استفاده شد که در آموزش قبلی بر آن پرداختیم، است.

ابتدا، یک نقطه ساکن مناسب یا “نقطه – Q ” برای بایاس صحیح مدار تقویت کننده JFET با پیکربندی های تقویت کننده واحد منبع مشترک (CS)، تخلیه مشترک (CD) یا دنبالکننده منبع (SF) و گیت مشترک (CG) موجود برای اکثر قطعات FET نیاز است تا پیدا شود.

این 3 پیکربندی های تقویتکننده JFET متناظر با امیتر مشترک، دنبال کننده امیتر و پیکربندی های بیس مشترک هستند که از ترانزیستورهای دو قطبی استفاده میکند. در این آموزش درباره تقویتکننده FET بر تقویتکننده JFET منبع مشترک معروف که اکثرا به صورت گسترده در طراحی تقویت کننده JFET استفاده میشود خواهیم پرداخت.

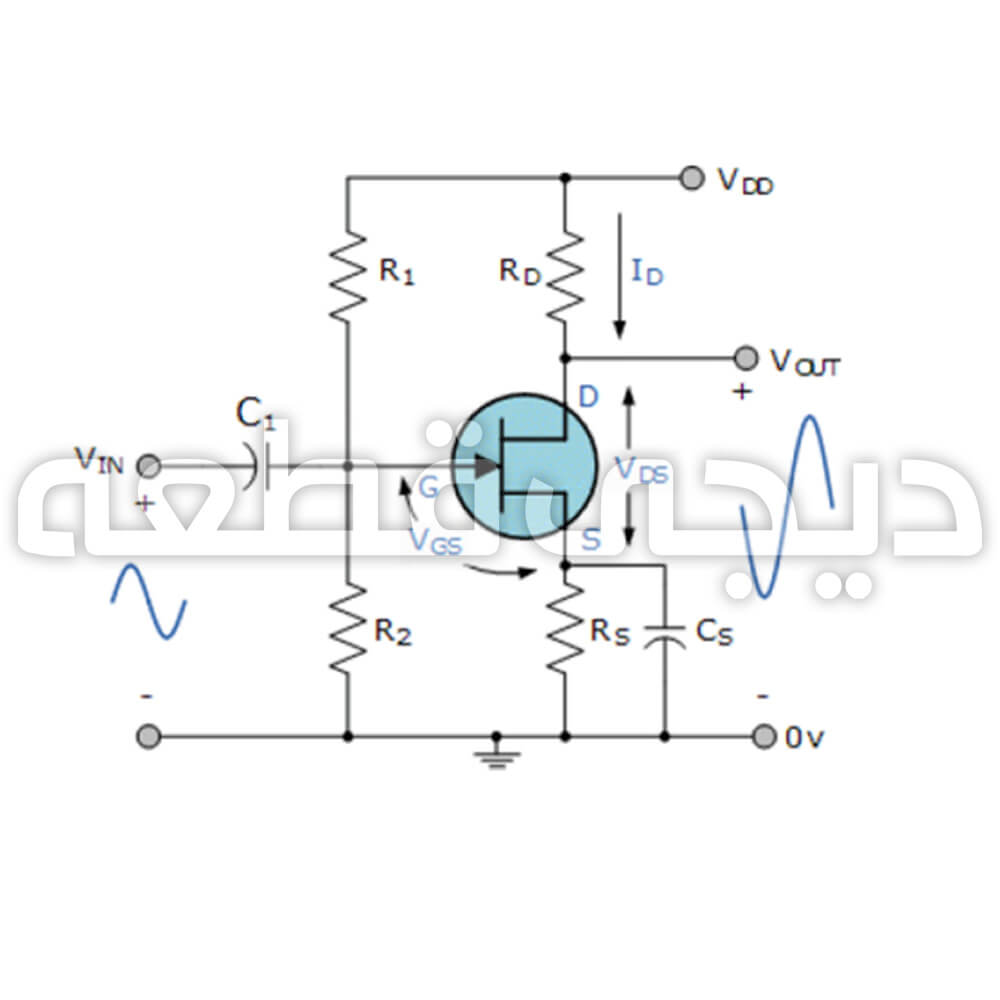

پیکربندی مدار تقویتکننده JFET منبع مشترک زیر را در نظر بگیرید.

تقویت کننده JFET منبع مشترک

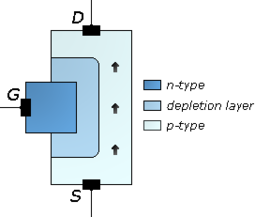

مدار تقویتکننده شامل یک JFET N کاناله است اما قطعه همچنین میتواند یک MOSFET حالت -تهی N – کانال باشد به طوری که نمودار مدار همان خواهد شد تنها یک تفاوت در FET است که در یک پیکربندی منبع مشترک وصل شده است. ولتاژ گیت JFET Vg از طریق شبکه تقسیمکننده پتانسیل که توسط مقاومتهای R1 و R2 تنظیم شده، بایاس شده است و برای عمل کردن درون ناحیه اشباع آن که معادل با ناحیه فعال ترانزیستور پیوندی دوقطبی است، بایاس میشود.

برخلاف یک مدار ترانزیستور دوقطبی، پیوند FET به صورت مجازی هیچ جریان گیتی را نمیگیرد و به گیت اجازه رفتار مانند یک مدار باز را میدهد. سپس هیچ منحنی مشخصات ورودی نیاز نیست. میتوان JFET را با ترانزیستور پیوندی دوقطبی (BJT) در جدول زیر مقایسه کرد.

مقایسه JFET با BJT

از آنجا که JFET، ان یک قطعه حالت تهی است و به صورت نرمال “روشن” است یک ولتاژ گیت منفی با توجه به منبع برای مدوله کردن یا کنترل جریان تخلیه نیاز است. این ولتاژ منفی میتواند با بایاس کردن از یک ولتاژ تغذیه توان جداگانه یا به وسیله یک آرایش خود بایاس تا زمانی که یک جریان ثابت در JFET شارش یابد حتی هنگامی که هیچ سیگنال ورودی فعلی وجود ندارد و Vg یک بایاس معکوس از پیوند pn گیت – تغذیه را به دست میآورد مهیا شود.

در مثال ساده ما، بایاس از یک شبکه تقسیمکننده پتانسیل که به سیگنال ورودی اجازه تولید یک افت ولتاژ در گیت را با افزایش ولتاژ در گیت با یک سیگنال سینوسی را میدهد، مهیا شده است. هر جفت مناسب مقادیر مقاومت در نسبتهای صحیح ولتاژ بایاس صحیح را تولید خواهد کرد بنابراین ولتاژ گیت بایاس DC ،Vg به صورت زیر است:

توجه داشته باشید که این رابطه تنها نسبت مقاومتهای R1 و R2 است اما برای بهرهگیری از مزیت امپدانس ورودی بسیار بالا JFET همانند کاهش اتلاف توان در مدار، ما نیاز به ایجاد مقادیر بالای مقاومتها تا حد ممکن داریم، مقادیر 1MΩ تا 10MΩ رایج هستند.

سیگنال ورودی (Vin) تقویتکننده JFET منبع مشترک بین پایانه گیت و ریل ولتاژ صفر اعمال شده است. با یک مقدار ثابت ولتاژ گیت Vg اعمال شده، JFET در داخل “ناحیه اهمی” خود مانند یک قطعه مقاومتی خطی عمل میکند. مدارتخلیه شامل مقاومت بار Rd است. ولتاژ خروجی Vout در دوسر این مقاومت بار گسترده شده است.

بازده تقویتکننده JFET منبع مشترک میتواند با اضافه کردن یک مقاومت Rs در پایه منبع با همان شارش جریان تخلیه از این مقاومت بهبود یابد. مقاومت Rs همچنین برای تنظیم “نقطه-Q” تقویتکنندههای JFET به کار میرود.

هنگامی که JFET به کاملا “روشن” تغییر یافت یک افت ولتاژ برابر با Rs×Id در دو سر این مقاومت گسترده شده است که پتانسیل پایانه منبع را به بالای 0 ولت یا سطح زمین میبرد. این افت ولتاژ دو سر Rs به دلیل جریان تخلیه یک شرط بایاس معکوس ضروری در دو سر مقاومت گیت R2 که موثرا فیدبک منفی تولید میکند مهیا میکند.

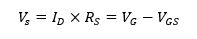

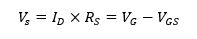

بنابراین برای نگه داشتن بایاس معکوس پیوند منبع-گیت، ولتاژ منبع Vs نیاز دارد تا بالاتر از ولتاژ گیت Vg باشد. درنتیجه این ولتاژ منبع به صورت زیر است:

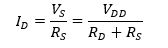

سپس جریان تخلیه Id همچنین برابر با جریان منبع Is است زیرا که “هیچ جریانی” وارد پایانه گیت نمیشود و این به صورت زیر ارائه میشود:

این مدار بایاس تقسیمکننده پتانسیل پایداری مدار تقویتکننده JFET منبع مشترک را زمانی که از یک تغذیه DC واحد در مقایسه به یک مدار بایاس ولتاژ ثابت تغذیه میشود بهبود میدهد. هر دو مقاومتها، Rs و خازن گذرگاه منبع Cs به صورت اساسی همان تابع را به عنوان مقاومت امیتر و خازن در مدار تقویت کننده ترانزیستور دوقطبی امیتر مشترک که ناما برای مهیا کردن پایداری خوب و ممانعت از یک کاهش در افت بهره ولتاژ است استفاده میکند. اگرچه، بهای داده شده برای یک ولتاژ گیت ساکن پایدار شده از ولتاژ تغذیه که در دو سر Rs افت کرده بیشتر است.

مقدار خازن گذرگاه منبع در فاراد عموما نسبتا بالای 100 میکروفاراد است و قطبی خواهد شد. این به خازن یک مقدار امپدانس بسیار کوچکتر کمتر از 10% هدایت gm (بهره نمایشی ضریب انتقال) مقدار قطعه را میدهد. در فرکانسهای بالا خازن گذرگاه ضرورتا مانند یک مدار اتصال کوتاه عمل میکند و منبع به صورت موثر مستقیما به زمین وصل خواهد شد.

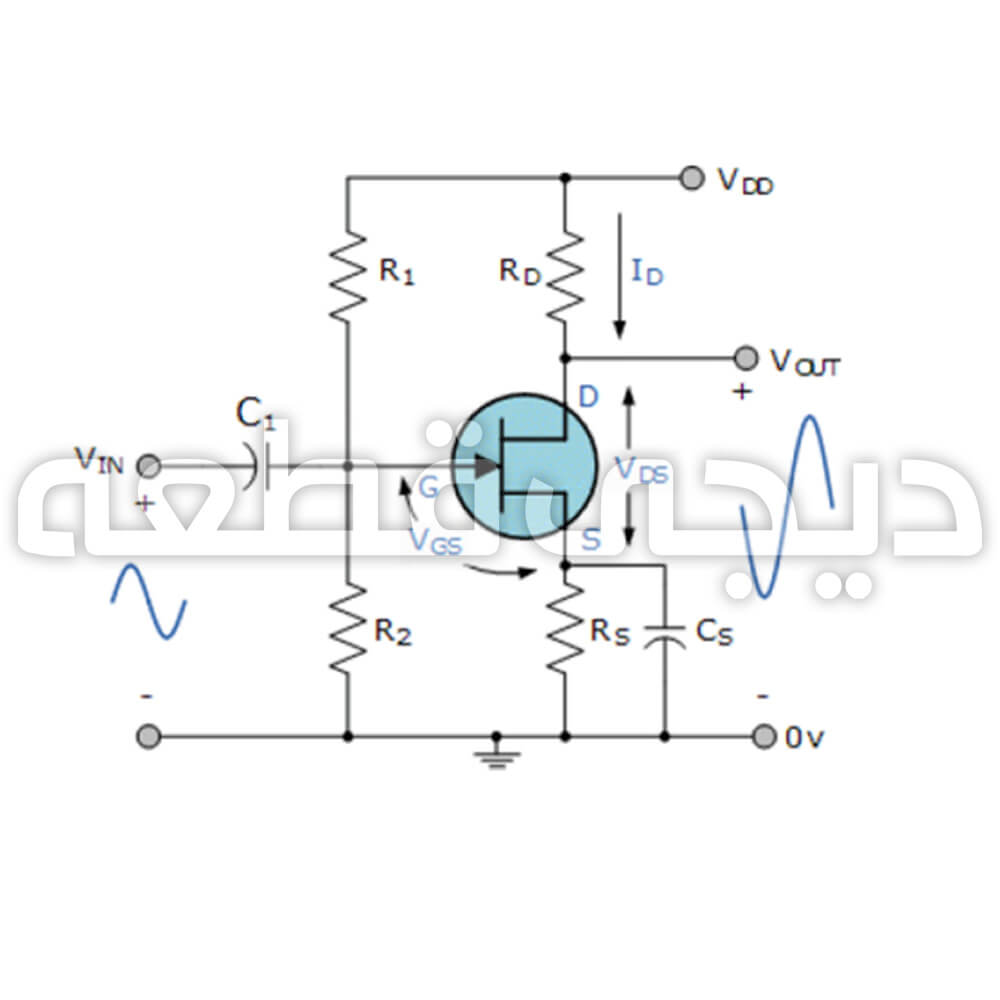

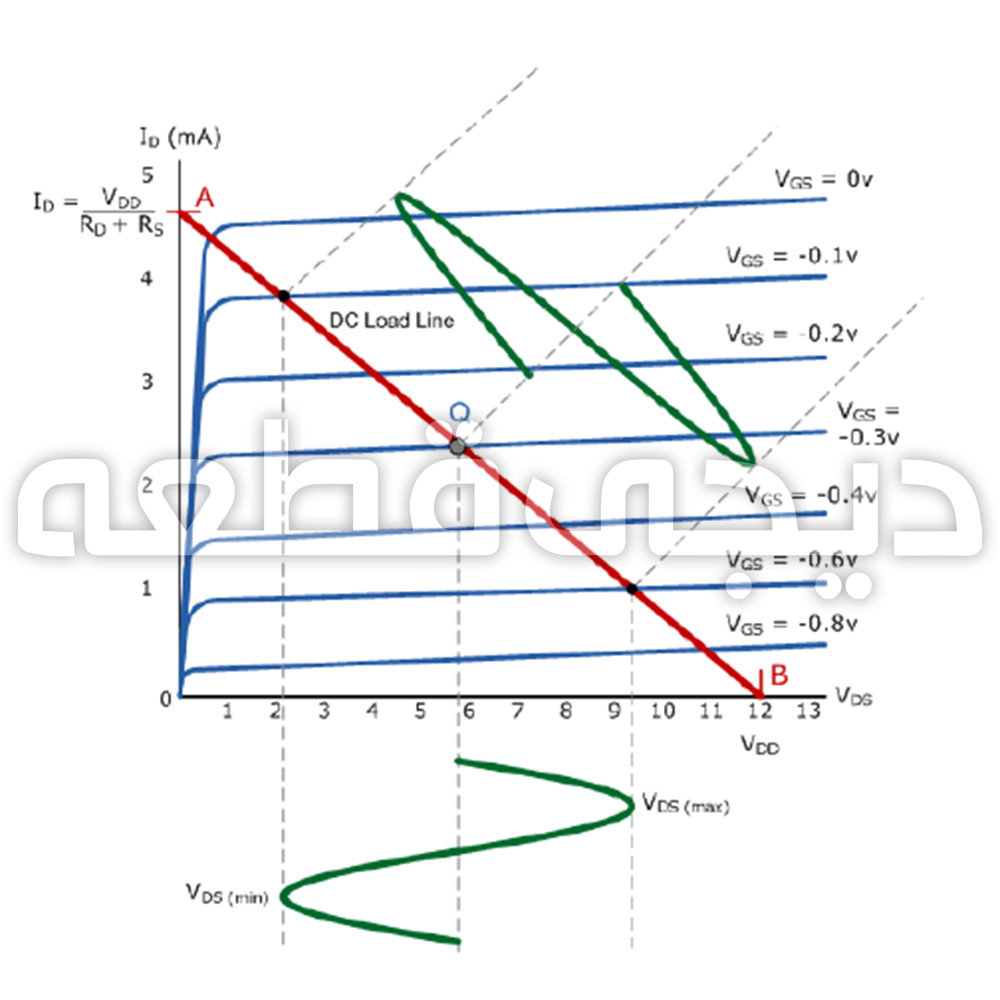

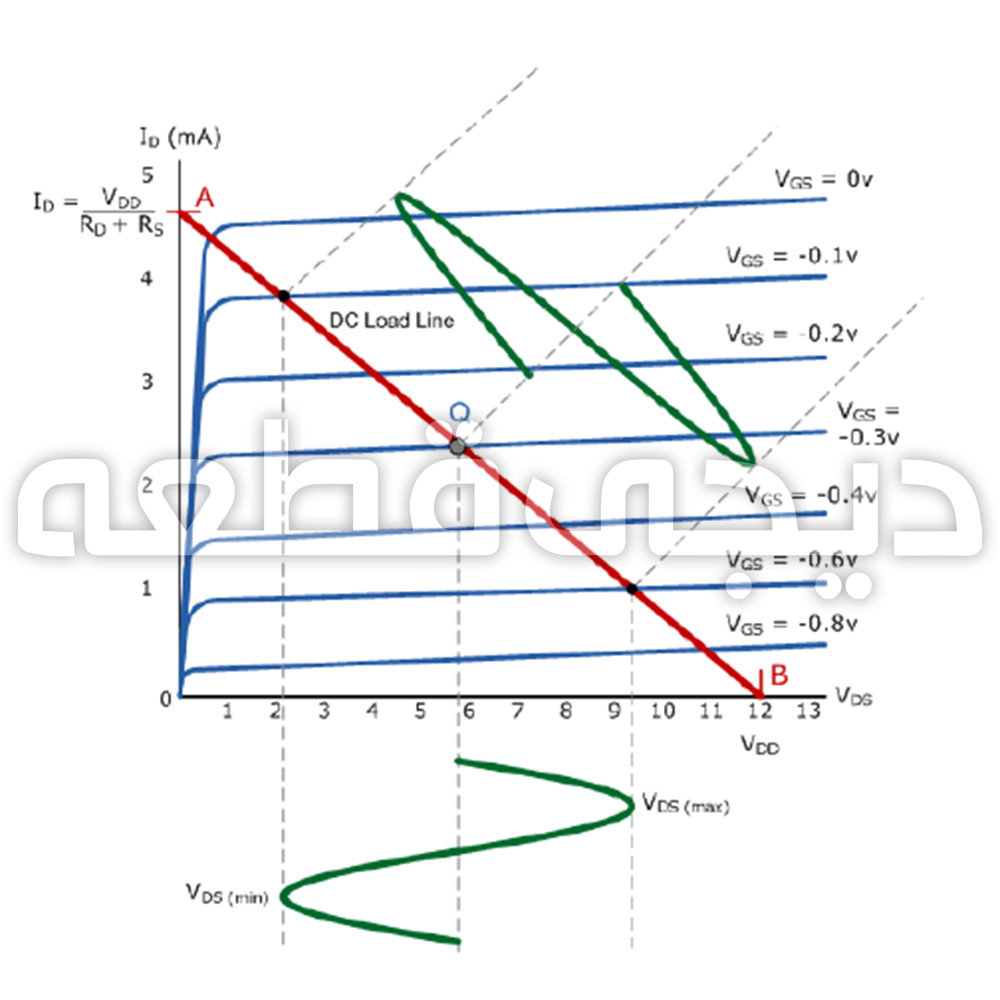

مدار پایه و مشخصات یک تقویتکننده JFET منبع مشترک بسیار شبیه به تقویتکننده امیتر مشترک است. خط بار DC با اتصال دو نقطه مرتبط به جریان تخلیه Id ساخته شده است و ولتاژ تغذیه Vdd خاطر نشان میکند که زمانی که Id=0:(Vdd=Vds) است و زمانی که Vdc=0: (Id=Vdd/RL) است. درنتیجه خط بار تقاطع منحنیها در نقطه Q به صورت زیر است.

منحنی مشخصات تقویت کننده JFET منبع مشترک

همانند مدار دوقطبی امیتر مشترک، خط بار DC برای تقویتکننده JFET منبع مشترک یک رابطه خط مستقیم که گرادیان آن برابر با -1/(Rd+Rs) است تولید میکند و آن محور Id عمودی را در نقطه A معادل با Vdd/(Rd+Rs) قطع میکند. انتهای دیگر خط بار محور افقی را در نقطه B که معادل با ولتاژ تغذیه Vdd است، قطع میکند.

موقعیت واقعی نقطه Q بر روی خط بار DC عموما در نقطه مرکز وسط خط بار (برای عملیات کلاس A) است و توسط مقدار متوسط Vg که به صورت منفی بایاس شده است زیرا که JFET یک قطعه حالت تهی است، تعیین میشود. مانند تقویتکننده امیتر مشترک دوقطبی خروجی تقویتکننده منبع مشترک 180 درجه با سیگنال ورودی اختلاف فاز دارد.

یکی از معایب استفاده از JFET حالت تهی این است که آنها نیاز دارند تا به صورت منفی بایاس شوند. اگر این بایاس به هر دلیلی با شکست مواجه شد ولتاژ منبع – گیت ممکن است افزایش یابد و مثبت شود و باعث افزایش در جریان تخلیه شود که منجر به شکست ولتاژ تخلیه Vd میشود.

همچنین مقاومت کانال بالا Rds(on) پیوند FET پیوند یافته با جریان تخلیه حالت پایدار ساکن بالا باعث میشود تا این قطعات داغ شوند بنابراین یک عایق اضافی نیاز است. اگرچه، اکثر مشکلات همراه استفاده از JFET ها میتواند به صورت زیاد با استفاده از قطعات ماسفت حالت بهبود کاهش یابد.

ماسفتها یا FET های نیمه رسانای اکسید متال دارای امپدانسهای ورودی بالاتر و مقاومت کانال پایین در مقایسه با JFET معادل هستند. همچنین آرایشات بایاس برای ماسفتها متفاوت هستند و ناگزیر ما آنها را برای قطعات N کانال به صورت مثبت و برای قطعات کانال P منفی بایاس میکنیم و هیچ جریان تخلیهای شارش نخواهد یافت، سپس متعاقبا یک ترانزیستور بدون ایمنی خواهیم داشت.

بهره توان و جریان تقویت کننده JFET

قبلا گفتیم که جریان ورودی Ig یک تقویتکننده JFET منبع مشترک بسیار کوچک است زیرا که امپدانس گیت Rg شدیدا بالا است. درنتیجه تقویتکننده JFET منبع مشترک دارای یک نسبت بسیار خوب بین امپدانسهای خروجی و ورودی خود است و برای هر مقدار جریان خروجی IOUT تقویتکننده JFET دارای بهره جریان Ai بسیار بالا خواهد بود.

به این دلیل، تقویتکنندههای JFET منبع مشترک به صورت شدید به صورت مدارهای تطبیق امپدانس ارزشمند هستند و یا به عنوان تقویتکنندههای ولتاژ استفاده میشوند. به همین ترتیب، از آنجا که: توان= ولتاژ در جریان (P=V×I) و ولتاژهای خروجی معمولا میلیولت یا حتی ولت هستند، بهره توان Ap همچنین بسیار بالا است.