فلیپ فلاپ نوع D ، یک فلیپ فلاپ اصلاح شده نوع ست، ریست به اضافه یک معکوس کننده برای جلوگیری از بودن ورودیهای S و R دریک سطح منطقی یکسان است. یکی از معایب اصلی این مدار دوپایا گیت SR NAND این است که شرط ورودی نامشخص SET=”0″ و RESET=”0″ ممنوع است.

فهرست مطالب

فلیپ فلاپ D

این وضعیت هر دو خروجی را مجبور به بودن در منطق “1” میکند، عمل قفل فیدبک را برجسته میکند، بطوریکه وقتی ورودی به سطح منطق “1” رفت، کنترل از دست خواهد رفت، درحالی که ورودی دیگر در سطح منطق “0” وضعیت حاصل قفل را کنترل میکند.

اما برای جلوگیری از رخ دادن این، یک معکوس کننده میتواند بین ورودیهای “ست” و “ریست” برای ایجاد نوع دیگر مدار فلیپ فلاپ معروف به یک قفل داده، فلیپ فلاپ تاخیر، دوپایا نوع D، فلیپ فلاپ نوع D یا تنها فقط یک فلیپ فلاپ D که بیشتر به این نام معروف است، متصل شود.

فلیپ فلاپ D تاکنون مهمترین فلیپ فلاپ ساعتدار است بطوریکه آن تضمین میکند که ورودیهای S و R هیچ وقت در یک زمان برابر با یکدیگر نمیشوند. فلیپ فلاپ نوع D از یک فلیپ فلاپ SR گیت دار با یک معکوس کننده اضافه شده بین ورودیهای S و R برای ممکن ساختن ورودی (داده) D واحد ساخته شده است.

سپس این ورودی داده واحد، با مارک “D” به جای سیگنال “ست” بکار میرود و معکوس کننده برای تولید ورودی “ریست” متمم بکار میرود بنابراین یک فلیپ فلاپ نوع D حساس به سطح از یک قفل SR حساس به سطح ایجاد میکند که اکنون S=D و R=NOT D است که نشان داده شده است.

مدار فلیپ فلاپ D

ما به یاد داریم که یک فلیپ فلاپ SR ساده نیازمند دو وردی است، یک برای “ست کردن” خروجی و یکی برای “ریست کردن” خرجی است. با اتصال یک معکوس کننده (گیت NOT) به فلیپ فلاپ SR میتوانیم فلیپ فلاپ را با استفاده از تنها یک ورودی “ست” و “ریست” کنیم بطوریکه اکنون دو سیگنال ورودی متمم یکدیگر هستند. این مکمل هنگامی که هر دو ورودی پایین باشد از ابهام ذاتی در قفل SR جلوگیری میکند، زیرا این حالت دیگر امکانپذیر نیست.

در نتیجه این ورودی واحد ورودی “داده” نامیده میشود. اگر این ورودی داده در بالا نگه داشته شود فلیپ فلاپ “ست” خواهد شد و هنگامی که آن پایین است، فلیپ فلاپ تغییر میکند و “ریست” میشود. اگرچه، این بیمعنی خواهد بود، زیرا که خروجی فلیپ فلاپ همیشه در هر پالس اعمال شده به ورودی داده آن تغییر خواهد کرد.

“فلیپ فلاپ D” تا زمانی که ورودی ساعت بالا است خروجی را چه سطح منطقی به ترمینال داده آن اعمال شده باشد، ذخیره خواهد کرد. یکبار که ورودی ساعت به پایین رفت ورودیهای “ست” و “ریست” فلیپ فلاپ هر دو در سطح منطق “1” نگه داشته و بنابراین آن وضعیت را تغییر نخواهد داد و هر دادهای که در خروجی خود قبل از اینکه گذر زمان صوت گیرد ذخیره میکند. در بیان دیگر، خروجی در هر دو سطح “0” یا “1” قفل شده است.

جدول درستی فلیپ فلاپ نوع D

توجه داشته باشید که ↓ و ↑جهت پالس ساعت را نشان میدهد بطوریکه فلیپ فلاپ نوع D بصورت تریگر شده در لبه فرض شده است.

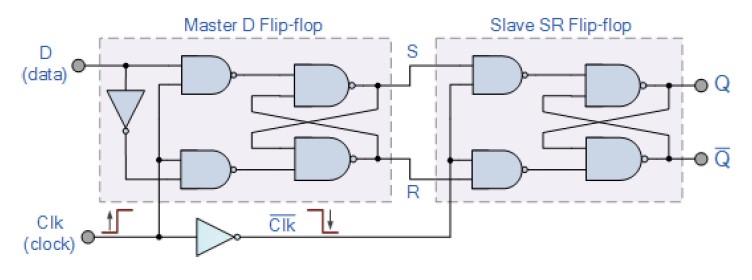

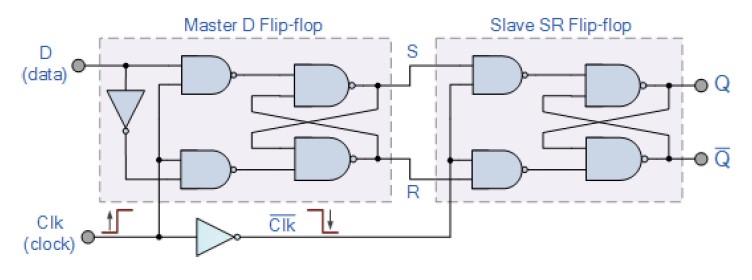

فلیپ فلاپ D مستر-اسلیو

فلیپ فلاپ نوع D میتواند بیشتر توسط اضافه کردن فلیپ فلاپ SR دومی به خروجی آن که بر سیگنال ساعت متمم برای تولید یک “فلیپ فلاپ نوع D مستر اسلیو” فعال شده است، بهبود یابد. در به پیشرو سیگنال ساعت (پایین به بالا) مرحله اول، “مستر” موقعیت ورودی را در D قفل میکند در حالیکه حالت خروجی غیر فعال شده است.

در لبه دنباله سیگنال ساعت (بالا به پایین) مرحله دوم “اسلیو” اکنون فعال شده است و بر خروجی از اولین مدار اصلی قفل می شود. سپس به نظر میرسد که مرحله خروجی در لبه منفی پالس ساعت تریگر شده است. “فلیپ فلاپ نوع D مستر اسلیو” میتوانند توسط سری کردن با هم دو قفل با فازهای ساعت مخالف ساخته شوند که نشان داده شده است.

مدار فلیپ فلاپ D مستر اسلیو

از بالا دیده میشود که در لبه پیشرو پالس ساعت، فلیپ فلاپ مستر داده را از ورودی D داده بارگذاری میکنند، درنتیجه مستر “روشن” است. با لبه دنباله پالس ساعت، فلیپ فلاپ اسلیو داده را بار گذاری میکند در نتیجه اسلیو “روشن” است. سپس یک فلیپ فلاپ “روشن” خواهد بود و دیگر “خاموش” است اما هر دو مستر و اسلیو در یک زمان هیچ گاه “روشن” نمیشوند. در نتیجه، خروجی Q نیازمند مقدار D هستند تنها زمانی که یک پالس کامل 0-1-0 به ورودی ساعت اعمال شده باشد.

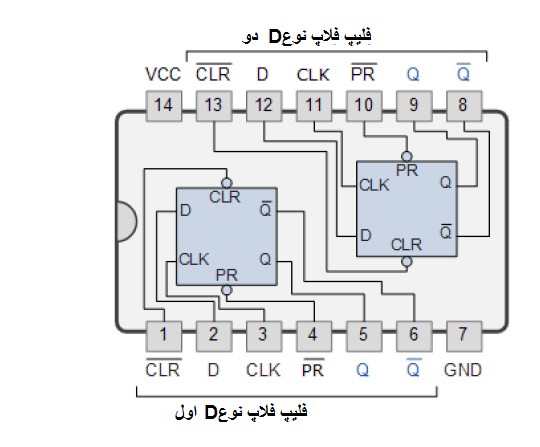

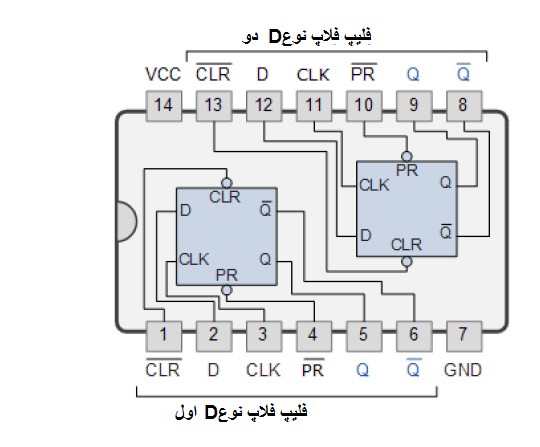

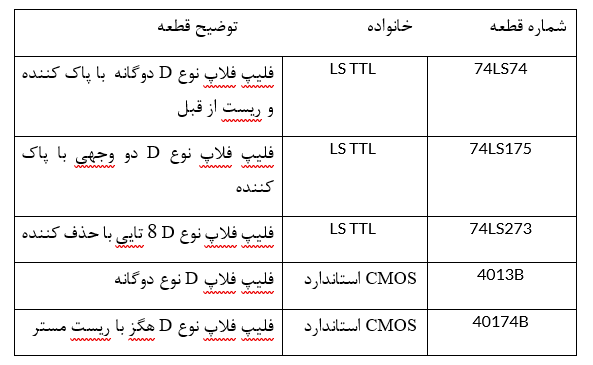

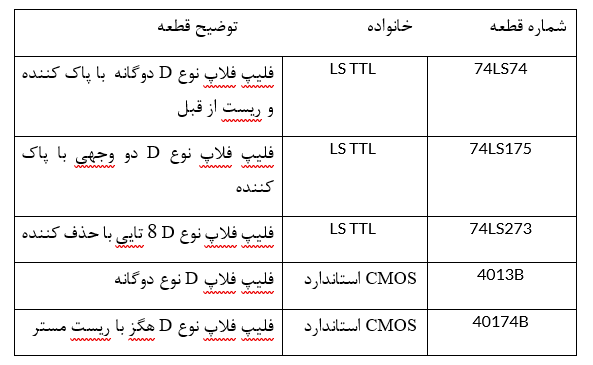

آی سی های فلیپ فلاپ D متفاوت زیادی در هر دو بسته CMOS و TTL وجود دارد بطوریکه رایجترین 74LS74 است که آی سی فلیپ فلاپ D دوگانه است که شامل دو دوپایا نوع D مستقل درون یک تراشه واحد است که فلیپ فلاپ های تغییر مستر-اسلیو یا واحد را میسازد. آی سی های فلیپ فلاپ D دیگر شامل فلیپ فلاپ D هگز 74LS174 با ورودی پاک کردن مستقیم، فلیپ فلاپ D دووجهی 74LS175 با خروجیهای متمم و فلیپ فلاپ های نوع D هشت تایی 74LS273 است که شامل هشت فلیپ فلاپ نوع D با یک ورودی پاک کننده در یک بسته واحد است.

فلیپ فلاپ نوع D دوگانه 74LS74

آی سی های معروف فلیپ فلاپ نوع D

استفاده از فلیپ فلاپ D برای تقسیم فرکانسی

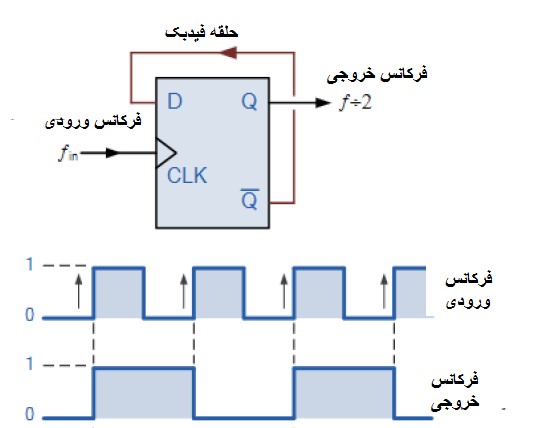

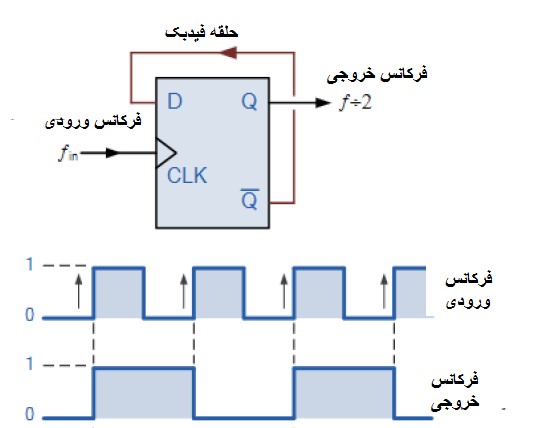

یک کاربرد اصلی از فلیپ فلاپ نوع D تقسیم کننده فرکانسی است. اگر خروجی در یک فلیپ فلاپ نوع D مستقیما به ورودی D وصل شود، یک فیدبک حلقه بسته ارائه میکند، پالسهای ساعت پی در پی باعث “تغییر” دو پایا در هر دو سیکل ساعت خواهند شد.

در آموزش شمارندهها دیدیم که چگونه میتوان از قفل داده به عنوان “تقسیم کننده دودویی” یا “تقسیم کننده فرکانس” برای تولید یک مدار شمارنده “تقسیم به-2” استفاده کرد، یعنی خروجی نصف فرکانس پالس ساعت است. با قرار دادن یک حلقه بازخورد در اطراف فلیپ فلاپ نوع D، نوع دیگر مدار فلیپ فلاپ میتواند ساخته شود که یک فلیپ فلاپ نوع T یا بیشتر دوپایا نوع T نامیده میشود که میتواند به عنوان یک مدار تقسیم شده بر 2 در شمارندههای دودویی بکار رود که در زیر نشان داده شده است.

شمارنده تقسیم شده بر 2

از شکل موجهای فرکانس بالا دیده میشود که، با “فید بک کردن خروجی از Q بار به ترمینال ورودی D، پالس های خروجی در Q یک فرکانسی دارند که دقیقا نصف (f/2) فرکانس ساعت ورودی (fIN) است. در بیان دیگر، مدار تقسیم فرکانسی تولید میکند، زیرا که اکنون آن فرکانس ورودی را با فاکتور دو (یک اکتاو) بصورت Q=1 در هر دو سیکل ساعت تقسیم میکند.

فلیپ فلاپ D به عنوان قفل

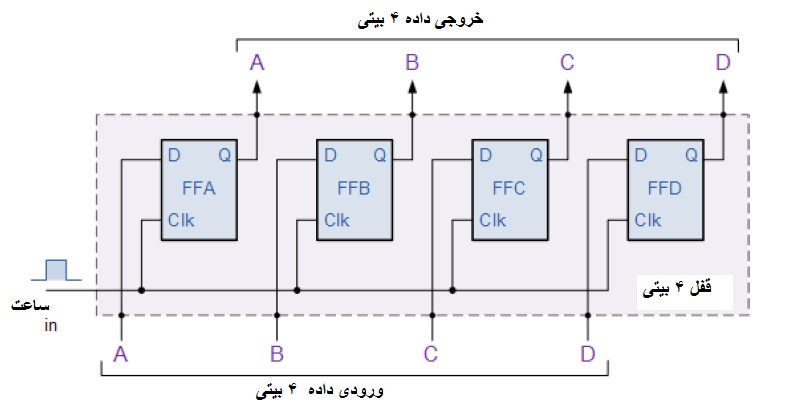

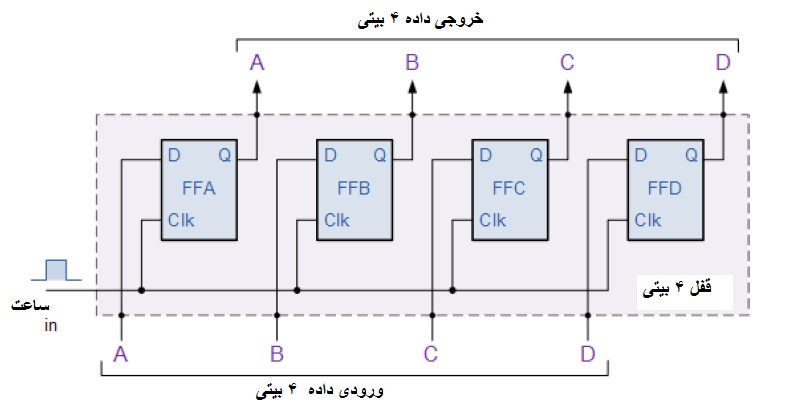

همانند تقسیم فرکانسی، کاربرد مفید دیگر فلیپ فلاپ D به عنوان یک قفل داده است. یک قفل داده میتواند به عنوان یک قطعه برای نگه داشتن و حفظ کردن وجود داده بر روی ورودی داده خود است، بنابراین یک بیت مانند یک قطعه حافظه تک بیت عمل میکند و آی سی هایی مانند TTL 74LS74 یا CMOS 4042 در قالب چهار گوش دقیقا برای این هدف موجود هستند. با اتصال به هم این 4 تا، قفل داده تک بیتی، بنابراین تمام ورودیهای ساعت آنها به یکدیگر وصل میشوند و در یک زمان “هم زمان” میشوند، یک قفل داده “4 بیتی” میتواند مانند شکل زیر ساخته شود.

قفل داده 4 بیتی

قفل داده شفاف

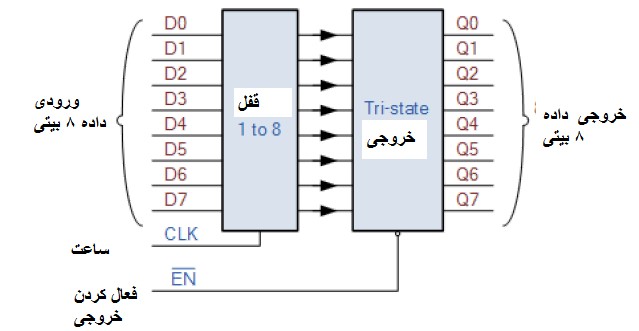

قفل داده یک قطعه بسیار مفید در مدارهای الکترونیکی و رایانه ای است. آنها میتوانند به گونهای طراحی شوند که امپدانس خروجی بسیار بالایی در هر دو خروجی Q و خروجی (Q بار) معکوس یا مکمل آن داشته باشند تا در هنگام استفاده به عنوان بافر، درگاه I / O، درایور باس دو جهته یا حتی درایور نمایشگر، تاثیر امپدانس بر روی مدار متصل را کاهش دهد.

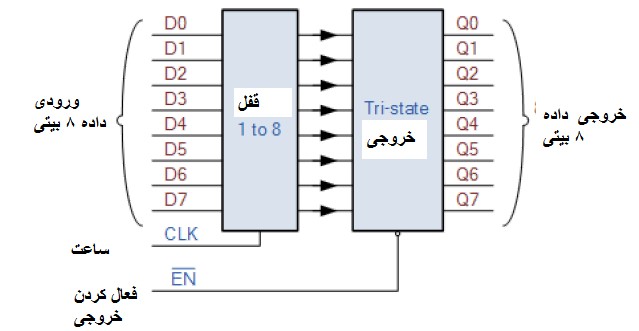

اما یک قفل داده “1 بیتی” برای استفاده به خودی خود چندان کاربردی نیست و در عوض، IC های موجود شامل 4، 8، 10، 16 یا حتی 32 قفل داده مجزا در یک بسته IC جداگانه از نظر تجاری در دسترس قرار دارد و یک قطعه آی سی این چنینی قفل شفاف نوع D هشت تایی 74LS373 است.

هشت قفل داده مستقل یا دوپایا از 74LS373 فلیپ فلاپ های نوع D “شفاف” هستند، به این معنی که هنگامی که ورودی ساعت (CLK) در سطح منطق “1” بالا است (اما همچنین میتواند پایین فعال یاشد) خروجی در Q دادههای D داده را هدایت میکنند.

در این پیکربندی، گفته میشود که قفل “باز” است و مسیر از ورودی D بار تا خروجی Q بار بصورت “شفاف” ظاهر میشود زیرا که دادهها از آن بصورت غیر قابل مشاهده جاری میشود، از این رو نام آن قفل شفاف است.

هنگامی که سیگنال ساعت پایین در سطح منطقی “0” است، قفل “بسته” میشود و خروجی در Q بار در مقدار نهایی داده قفل میشود که آن قبل از اینکه سیگنال ساعت تغییر یابد نمایش داده شده است و دیگر در پاسخ به تغییر نمیکند.

قفل داده 8 بیتی

خلاصه فلیپ فلاپ نوع D

فلیپ فلاپ نوع D یا داده میتواند با استفاده از یک جفت از قفلهای SR پشت به پشت و اتصال یک معکوس کننده بین (گیت NOT) ورودیهای S و R برای ایجاد یک ورودی (داده) D واحد ساخته شود. مدار فلیپ فلاپ D پایه میتواند با اضافه کردن یک فلیپ فلاپ SR دومی به خروجی آن بیشتر بهبود یابد که آن در سیگنال ساعت متمم برای تولید قطعه ” فلیپ فلاپ D مستر- اسلیو” فعال شده است.

تفاوت بین قفل نوع D و یک فلیپ فلاپ نوع D این است که یک قفل سیگنال ساعتی برای تغییر وضعیت ندارد درحالی که یک فلیپ فلاپ همیشه دارد. فلیپ فلاپ D یک قطعه تریگر شده لبه است که داده ورودی را به Q بار بر لبه بالارونده یا پایین رونده ساعت انتقال میدهد. قفلهای داده قطعات حساس به سطح مانند قفل داده و قفل شفاف هستند.

در آموزش بعدی درباره مدارهای منطقی ترتیبی، بر اتصال به هم قفلهای داده برای تولید نوع دیگر مدار منطقی ترتیبی معروف به یک شیفت رجیستر که برای تبدیل داده موازی به داده سریال و برعکس بکار میرود، خواهیم پرداخت.