فهرست مطالب

مدارهای منطقی متوالی

مدارهای منطقی متوالی از فلیپ-فلاپ ها به عنوان عناصر حافظه استفاده میکند بطوریکه خروجی آنها به وضعیت ورودی وابسته است. برخلاف مدارهای منطقی ترکیبی که بسته به سیگنالهای واقعی که در آن زمان به ورودیهایشان اعمال میشوند، تغییر میکنند، مدارهای منطقی متوالی دارای نوعی “حافظه” ذاتی که در داخل آن ساخته شده، است.

به این معنا که مدارهای منطقی متوالی قادر به در نظر گرفتن وضعیت ورودی قبلی خود و همچنین مواردی که واقعا موجود هستند، است. مجموعه ای از تاثیر”قبل” و “بعد” با مدارهای متوالی همراه است.

به عبارت دیگر، وضعیت خروجی “مدار منطقی متوالی” تابعی از سه حالت “ورودی فعلی”، “ورودی گذشته” و / یا “خروجی گذشته” است. مدارهای منطقی متوالی این شرایط را به یاد میآورد و تا زمانیکه سیگنال ساعت بعدی یکی از وضعیت ها را تغییر دهد و به مدارهای منطقی متوالی “حافظه” بدهد، در حالت فعلی خود ثابت میماند.

مدارهای منطقی متوالی به طور کلی به عنوان قطعات دو حالته یا دستگاه دوپایا خوانده میشوند که می توانند خروجی یا خروجی های خود را در یکی از دو حالت اساسی، یک سطح منطقی “1” یا یک سطح منطقی “0” تنظیم کنند و به طور نامحدود در این وضعیت یا شرایط فعلی “قفل” باقی خواهند ماند (از این رو نام قفل) تا زمانی که برخی از پالس تریگر ورودی یا سیگنال دیگر اعمال شود که این باعث تغییر وضعیت دوباره دوپایا خواهد شد.

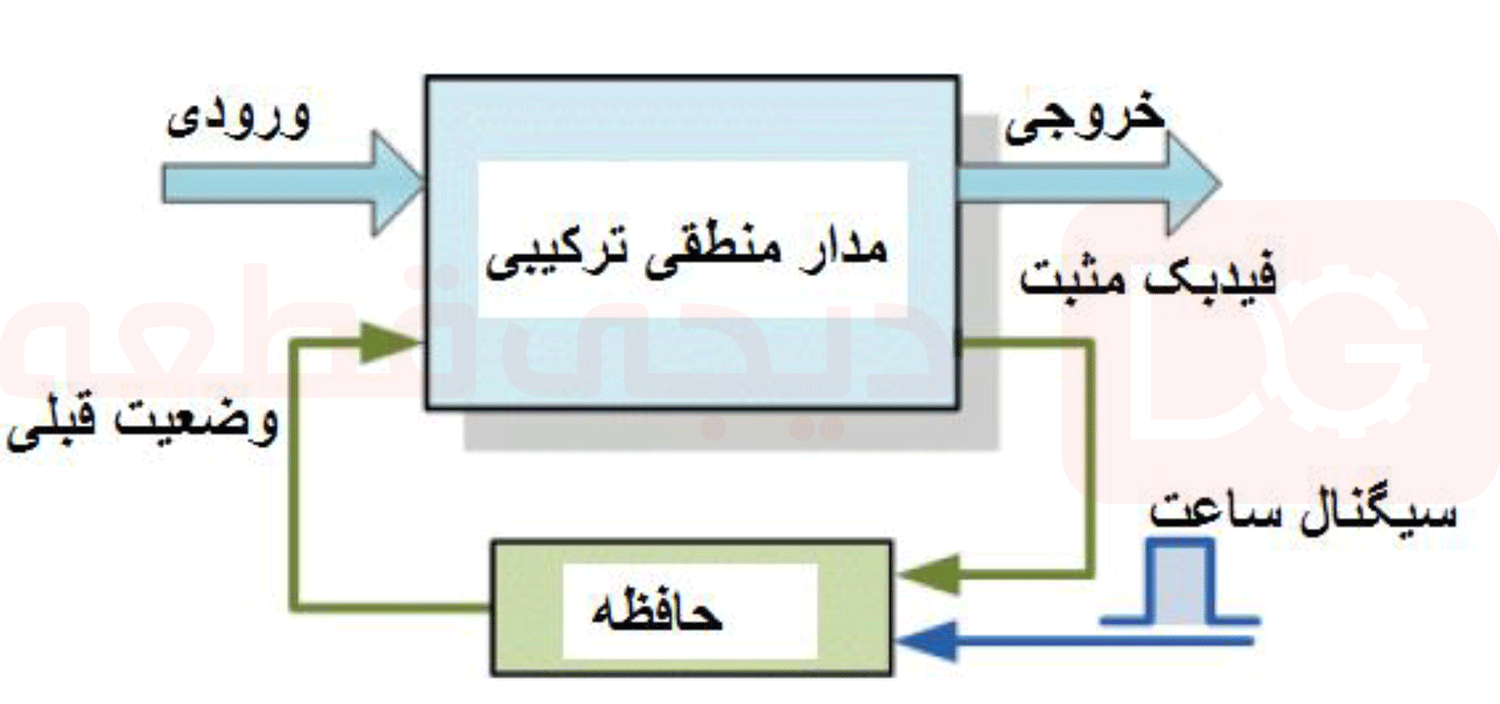

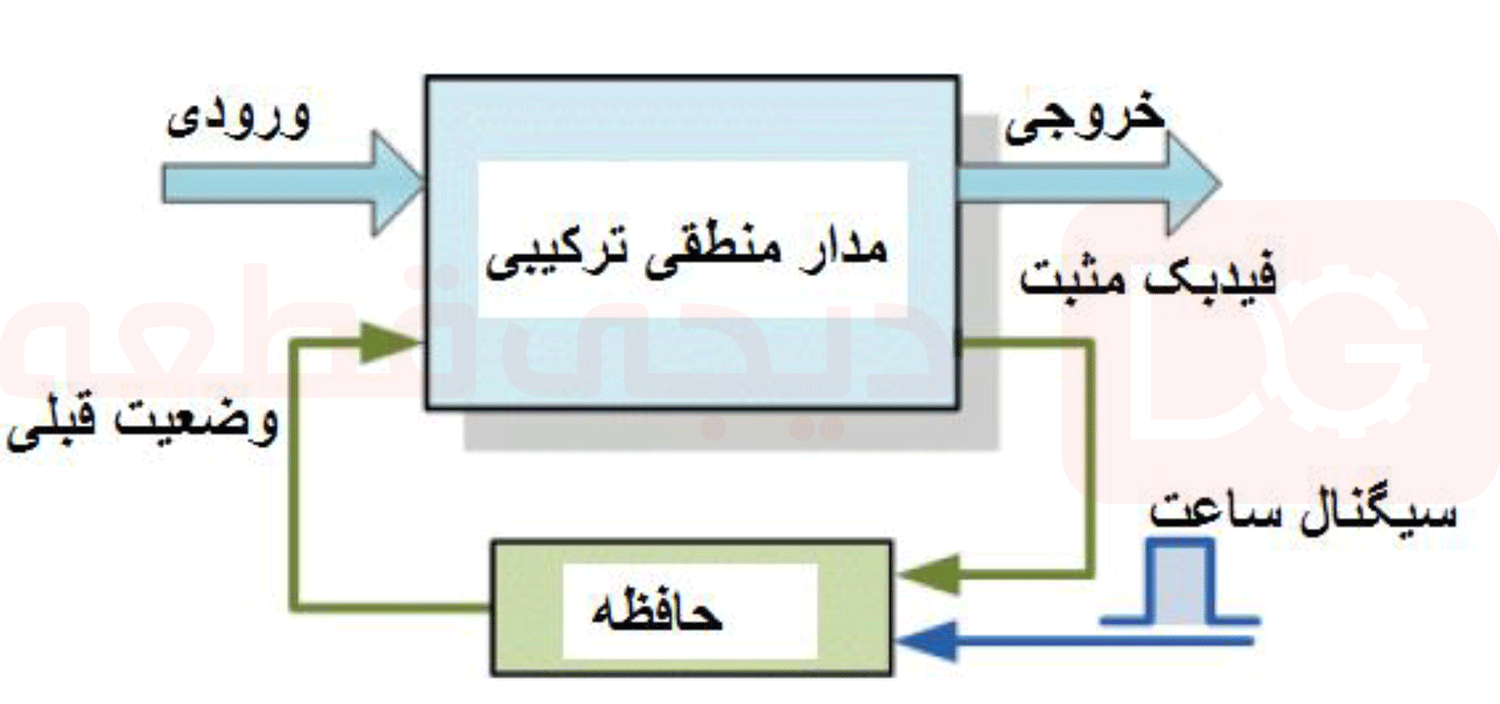

نمایش منطق متوالی

کلمه “متوالی” به این معنی است که اتفاق ها در یک “توالی” یکی پس از دیگری و در مدارهای منطقی متوالی، روی میدهند، سیگنال ساعت واقعی زمانی که چیزهای بعدی اتفاق بیافتند، را تعیین میکند. مدارهای منطقی متوالی ساده را می توان از مدارهای استاندارد دوپایا مانند: فلیپ-فلاپ ها، قفل ها و شمارنده ها ساخت به طوری که آنها با اتصال مستقیم دروازه های NAND عمومی و/ یا دروازه هایNOR به یکدیگر با روش ترکیبی خاص برای تولید مدار متوالی مورد نیاز ساخته میشوند.

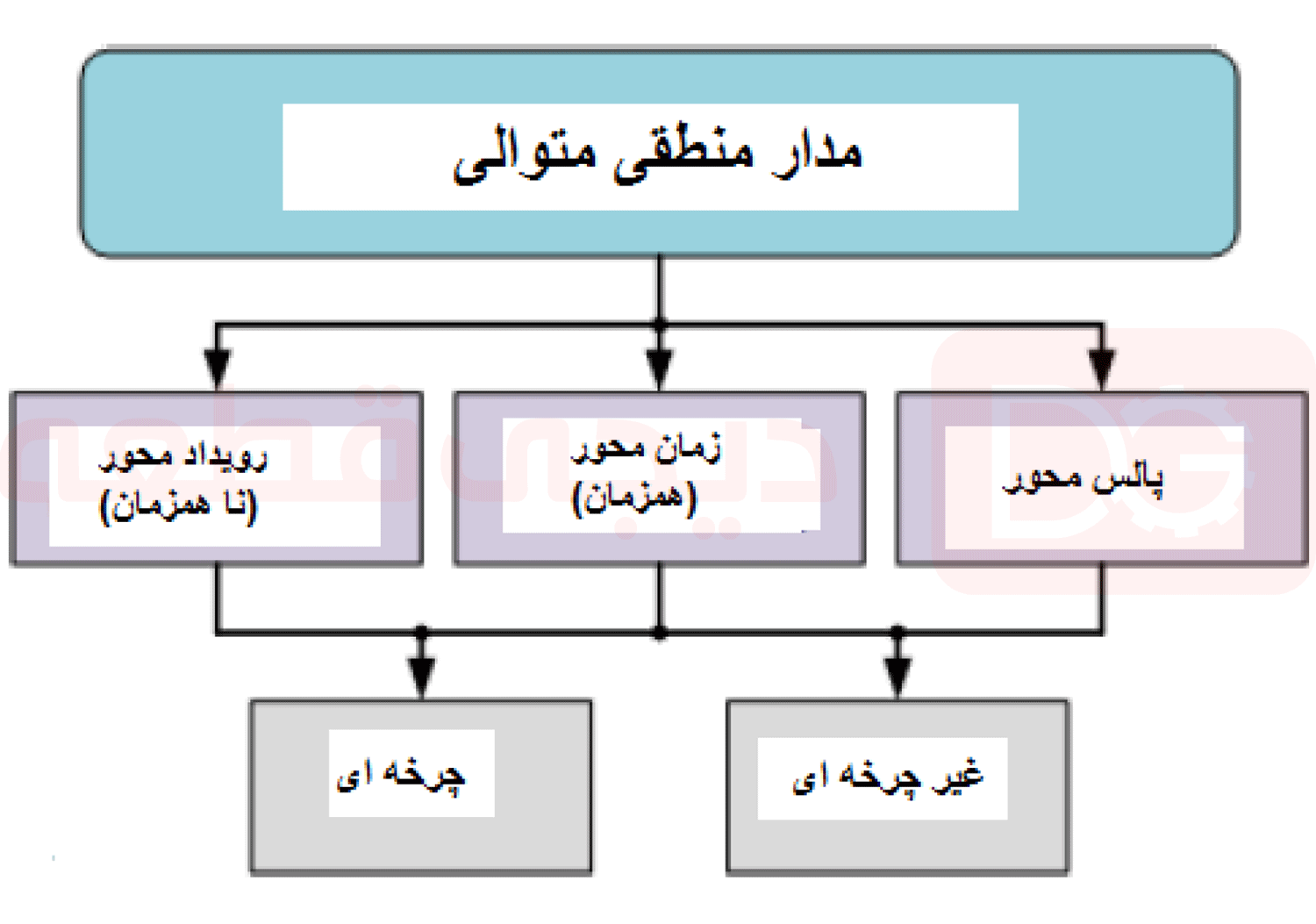

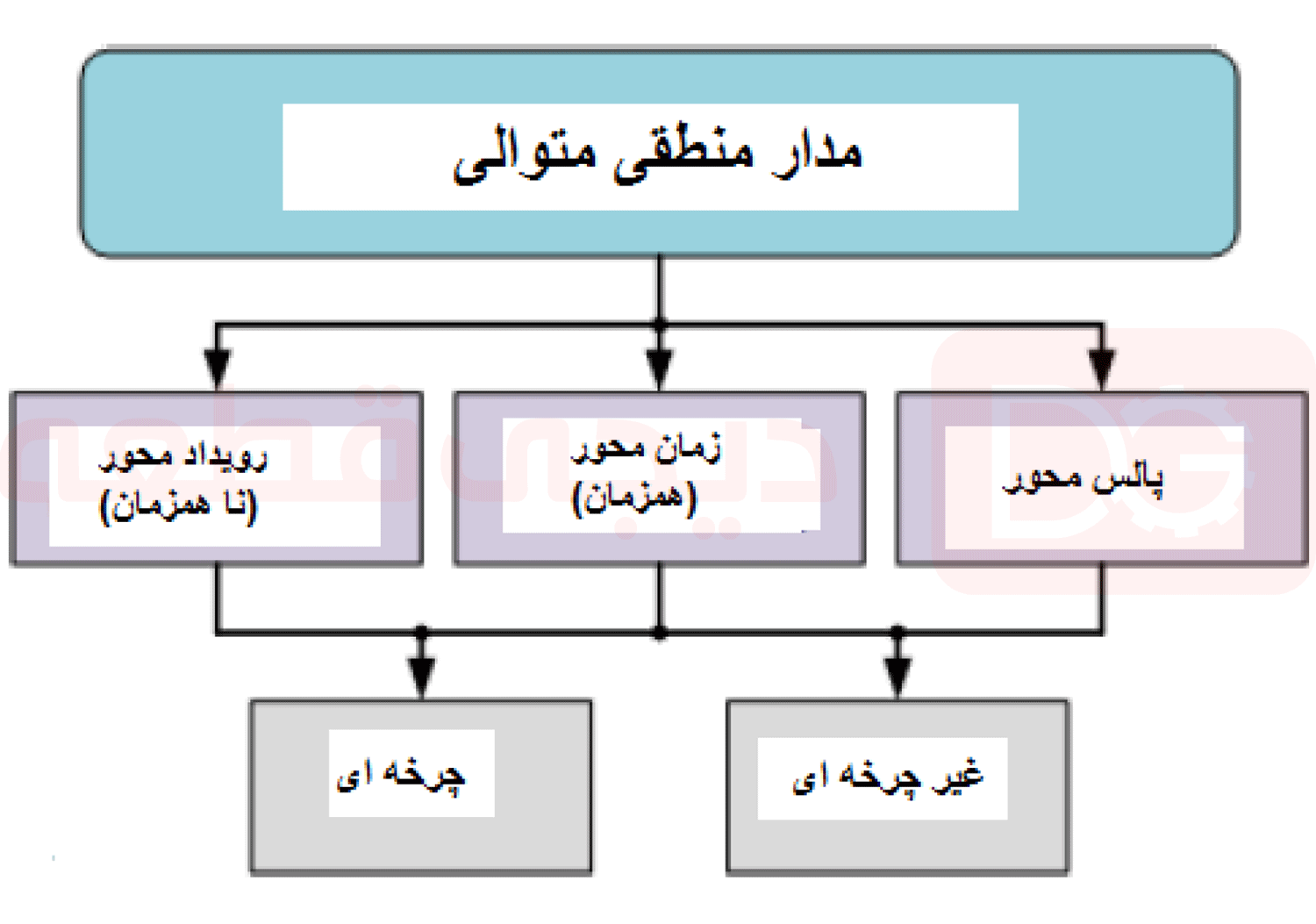

طبقه بندی منطق متوالی

همانطور که دروازه های منطقی استاندارد بلوک های ساختاری مدارهای ترکیبی هستند، قفل های دوپایا و فلیپ فلاپ ها بلوک ساختاری اصلی مدارهای منطقی متوالی هستند. مدارهای منطقی متوالی میتوانند برای تولید فلیپ-فلاپ های ترگیر شده لبه و یا مدارهای متوالی پیچیده تر مانند رجیسترهای ذخیره سازی، رجیسترهای فاصله، قطعات حافظه یا شمارنده ها ساخته شوند. در هر صورت، مدارهای منطقی متوالی می توانند در سه دسته اصلی زیر طبقه بندی شوند:

- رویداد محور – مدارهای ناهمزمان که هنگام فعال شدن، سریعا وضعیت را تغییر میدهند.

- زمان محور – مدارهای همزمان که با یک سیگنال ساعت خاص همزمان شده اند.

- پالس محور – که ترکیبی از این دو حالت است که به پالس های تریگر پاسخ میدهند.

همانند دو وضعیت اشاره شده در بالا، سطح منطق “1” و سطح منطق “0” یک عنصر سوم دارد که مدارهای منطقی متوالی را از همتایان منطق ترکیبی خود جدا میکند و با نام زمان معرفی شده است. مدارهای منطقی متوالی هنگامی که ریست میشوند به وضعیت پایدار اصلی خود باز میگردند و با حلقه ها یا مسیرهای بازخورد (فیدبک)، گفته می شود که در “چرخه ” هستند.

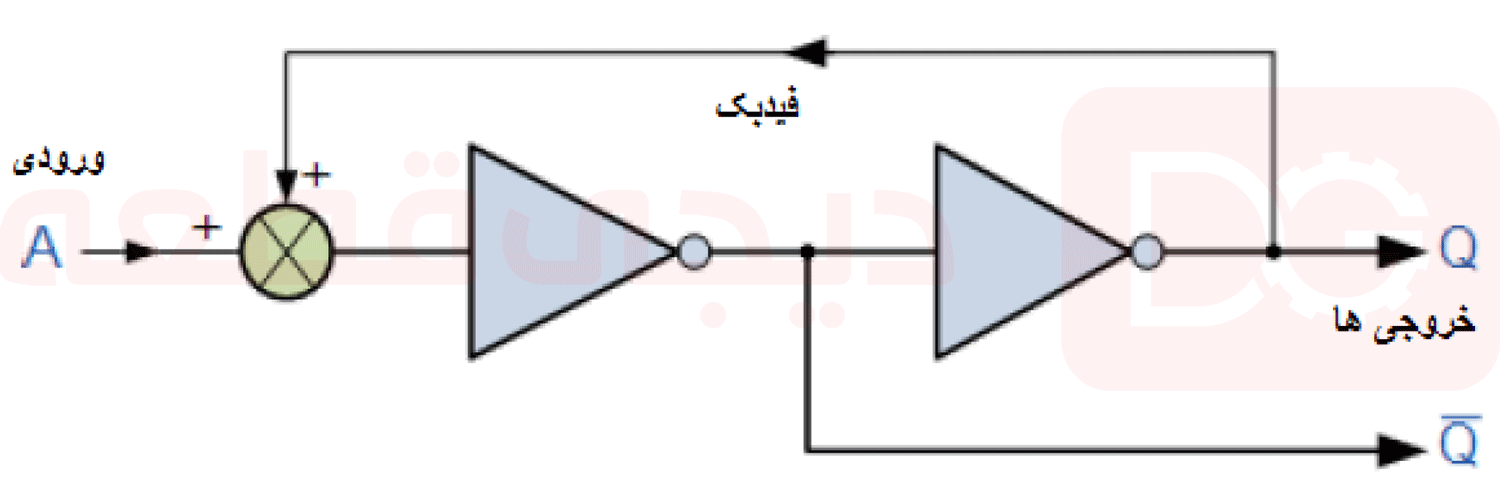

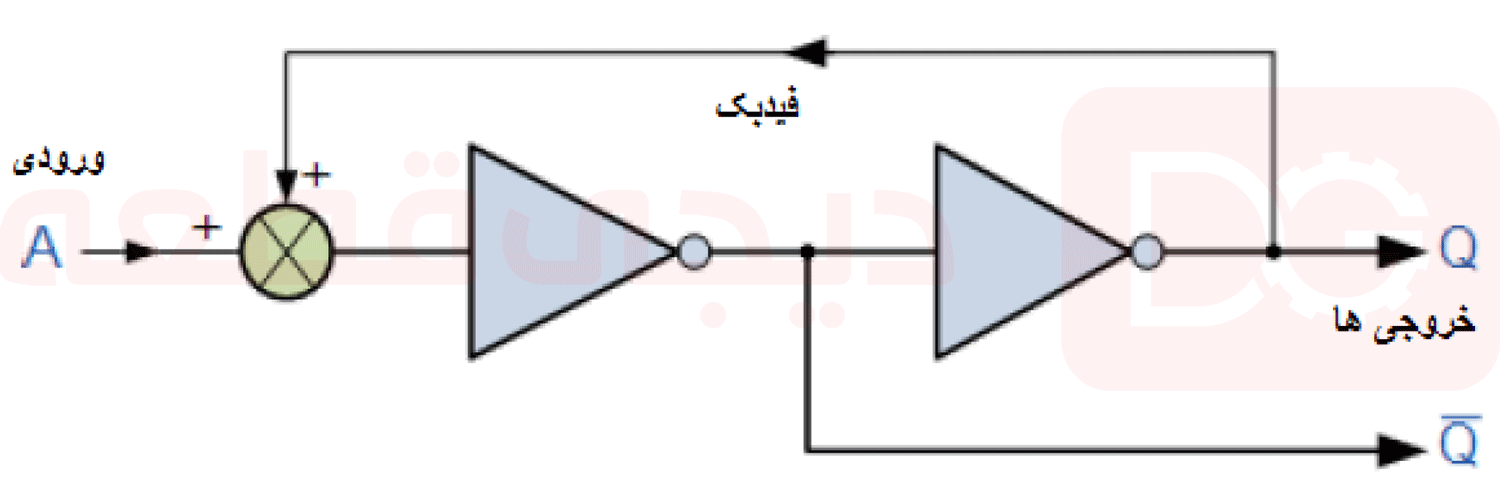

اکنون می دانیم که در مدارهای متوالی تغییرات تنها در کاربرد سیگنال ساعت که آن را همزمان میکند، ایجاد میشود، در غیر این صورت مدار ناهمزمان است و به ورودی بیرونی وابسته است. برای حفظ وضعیت فعلی خود، مدارهای متوالی به بازخورد تکیه میکنند و این زمانی که بخشی از خروجی به ورودی باز میگردد اتفاق میافتد و این به صورت زیر نشان داده می شود:

حلقه فیدبک متوالی

این دو اینورتر یا دروازه های NOT به صورت سری با خروجی Q در فیدبک به ورودی متصل می شوند. متأسفانه، این پیکربندی هرگز وضعیت را تغییر نمیدهد زیرا خروجی همیشه بصورت، یا “1” یا “0” یکسان خواهد بود و بصورت دائمی تنظیم می شود. با این وجود، می توانیم با بررسی اساسی ترین مؤلفه های منطقی متوالی، به نام فلیپ -فلاپ SR ، ببینیم چگونه فیدبک کار میکند.

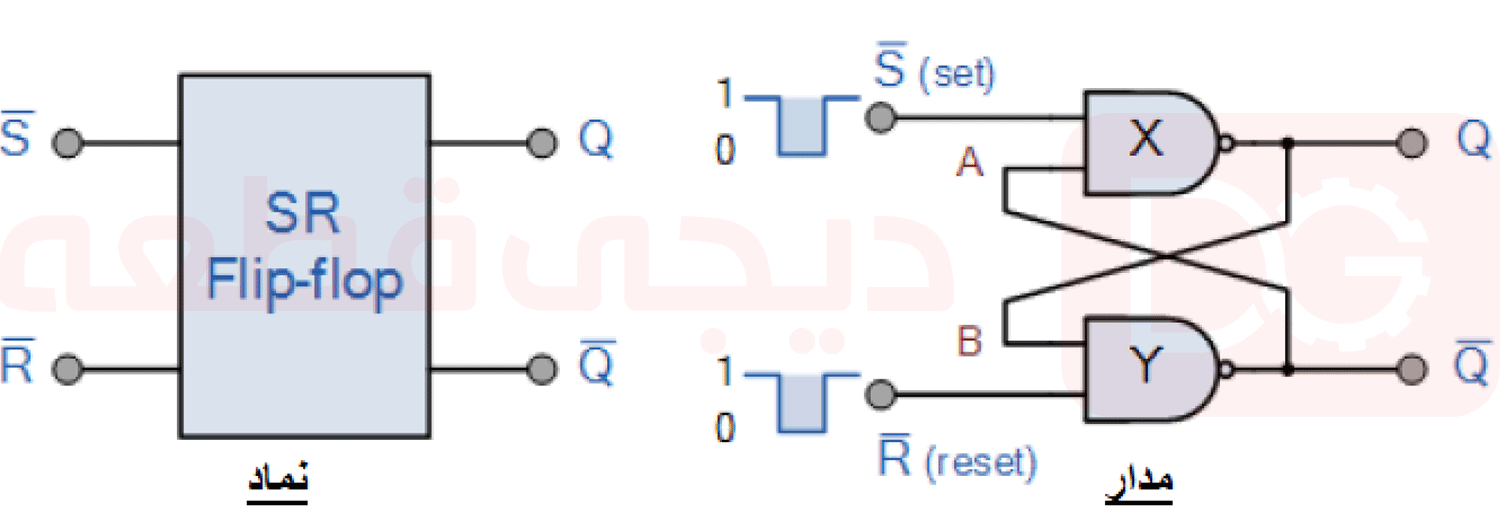

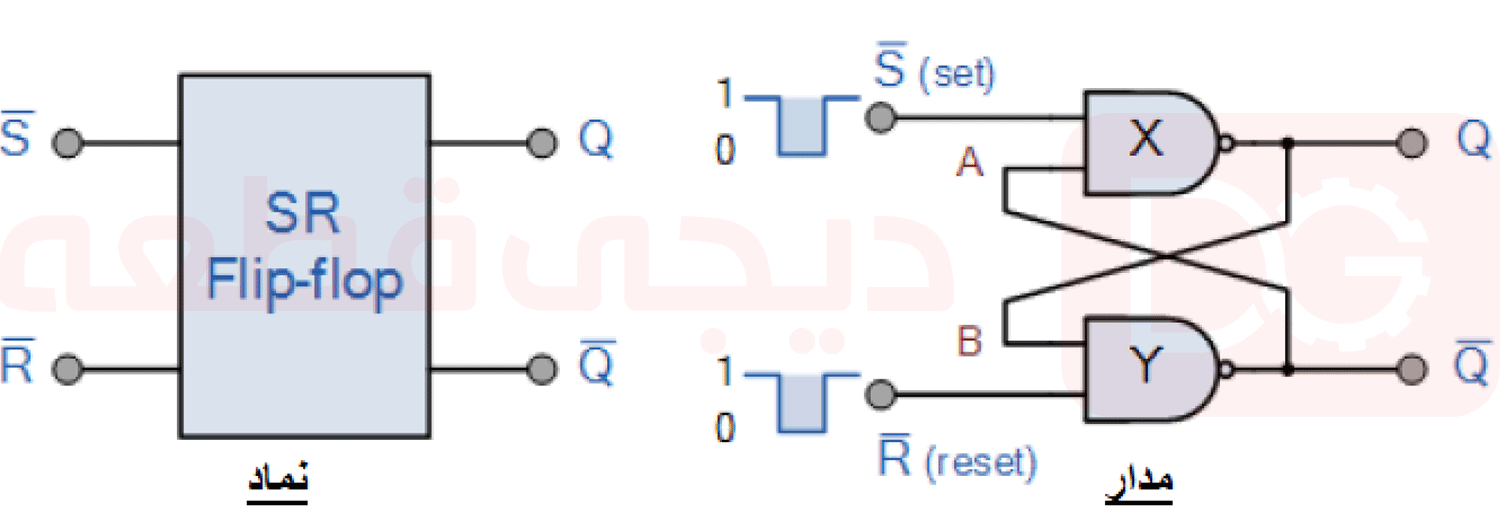

فلیپ-فلاپ SR

فلیپ-فلاپ SR که به عنوان قفل SR نیز شناخته می شود، می تواند به عنوان یکی از اساسی ترین مدار منطقی متوالی در نظر گرفته شود. این فلیپ فلاپ ساده در واقع یک قطعه دوپایا حافظه یک بیتی است که دارای دو ورودی است، یکی که دستگاه را “تنظیم” میکند (به معنی خروجی = “1”) و با S برچسب گذاری شده و دیگری که دستگاه را “ریست” میکند (به معنی خروجی = “0”) که با R برچسب گذاری شده است.

نماد SR مخفف “Set-Reset” است. ورودی ریست، فلیپ فلاپ را به وضعیت اولیه خود با خروجی Q باز می گرداند که بسته به این شرایط تنظیم / ریست، در سطح منطقی “1” یا منطق “0” خواهد بود.

یک مدار فیلیپ-فلاپ SR دروازه NAND، بازخوردی از خروجی های خود به ورودی های مخالف خود باز می گرداند و معمولاً در مدارهای حافظه برای ذخیره یک بیت داده واحد استفاده میشود. فلیپ –فلاپSR در واقع دارای سه ورودی، تنظیم، ریست و خروجی فعلی Q خود است، که به وضعیت یا پیشینه فعلی آن مربوط است. اصطلاح فلیپ-فلاپ به عملکرد واقعی قطعه مربوط می شود، زیرا که آن می تواند به یک وضعیت تنظیم منطقی “تنظیم” شود و یا به وضعیت ریست منطقی مخالف “بازگردانده ” شود.

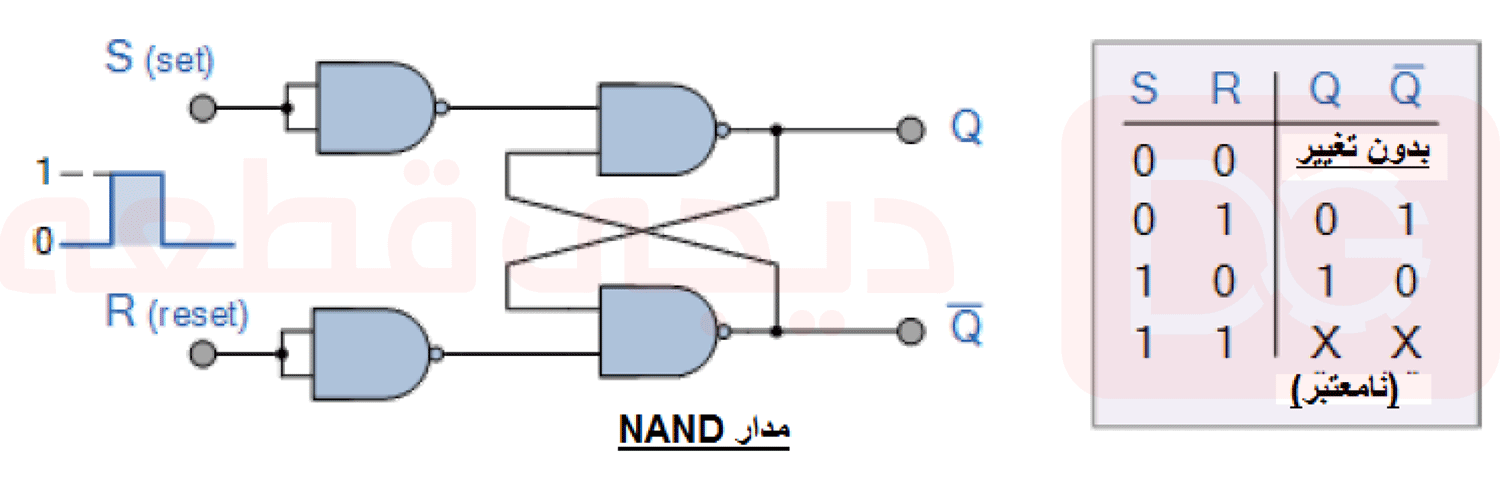

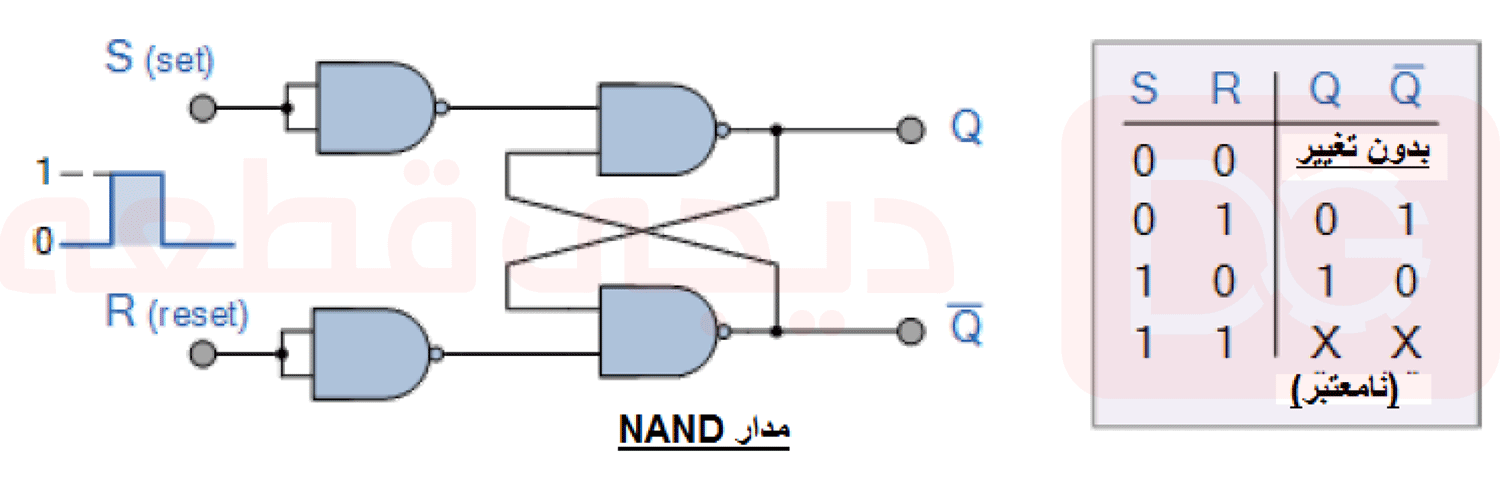

فلیپ-فلاپ SR دروازه NAND

ساده ترین راه برای ساخت فلیپ-فلاپ SR بیت سیگنال پایه، اتصال یک جفت دروازه NAND با ورودی 2 پیوندشده-متقاطع برای ایجاد یک دوپایا SR که همچنین به عنوان یک قفل دروازه NAND نوع SR فعال معروف است، که نشان داده شده است. به این ترتیب از هر خروجی به یکی از ورودی های دیگر دروازه NAND بازخورد وجود دارد. این قطعه از دو ورودی تشکیل شده است، یکی به نام Set (تنظیم) S و دیگری به نام Reset R (ریست) با دو خروجی متناظر Q و معکوسش یا مکمل (نه-Q) که در شکل زیر نیز نشان داده شده است.

فلیپ –فلاپ SR پایه

وضعیت تنظیم

مدار نشان داده شده در بالا را در نظر بگیرید. اگر ورودی R در سطح منطقی “0” باشد (R = 0) و ورودی S در سطح منطقی “1” (S = 1)، دروازه NAND Yحداقل در ورودی منطق “0” یکی از ورودی های خود را دارد، بنابراین، خروجی آن باید در سطح منطقی “1” باشد (اصول NAND Gate). خروجی نیز به ورودی “A” برگردانده میشود و بنابراین هر دو ورودی به دروازه NAND X در سطح منطقی “1” قرار دارند، بنابراین خروجی Q باید در سطح منطقی “0” باشد.

دوباره طبق اصول دروازه NAND، اگر ورودی ریست R وضعیت را تغییر دهد و به بالا و به منطق “1” با S برسد همچنان در سطح منطقی “1” باقی میماند، ورودی های دروازه NAND Yاکنون R = “1” و B = “0” هستند. از آنجا که یکی از ورودی های آن همچنان در سطح منطق “0” است، خروجی در همچنان بالا در سطح منطق “1” باقی میماند و هیچ تغییر وضعیتی وجود ندارد. بنابراین گفته می شود که مدار فلیپ-فلاپ “تنظیم” یا” قفل شده” با = “1” و Q = “0” است.

وضعیت ریست

در این وضعیت پایدار دوم، در سطح منطقی “0” است ، (نه Q = “0”) خروجی معکوس آن در Q در سطح منطقی “1” ، (Q = “1”) است و توسط R = “1” و” S = “0 بدست آمده است. از آنجا که دروازه X یکی از ورودی های خود را در منطق “0” دارد ، خروجی Q آن باید با منطق “1” برابر باشد (دوباره اصول دروازه NAND). خروجی Q به ورودی “B” برگردانده میشود، بنابراین هر دو ورودی به دروازه NAND Y در منطق “1” قرار دارند، بنابراین =” 0″ است.

اگر ورودی تنظیم S وضعیت را به منطق “1” تغییر دهد با ورودی R در منطق “1” باقی میماند، خروجی در سطح منطقی “0” پایین باقی میماند و هیچ تغییری دروضعیت وجود ندارد. بنابراین، وضعیت “ریست” مدارهای فلیپ-فلاپ همچنان قفل شده اند و می توانیم این عمل “تنظیم / ریست” را در جدول درستی زیر تعریف کنیم.

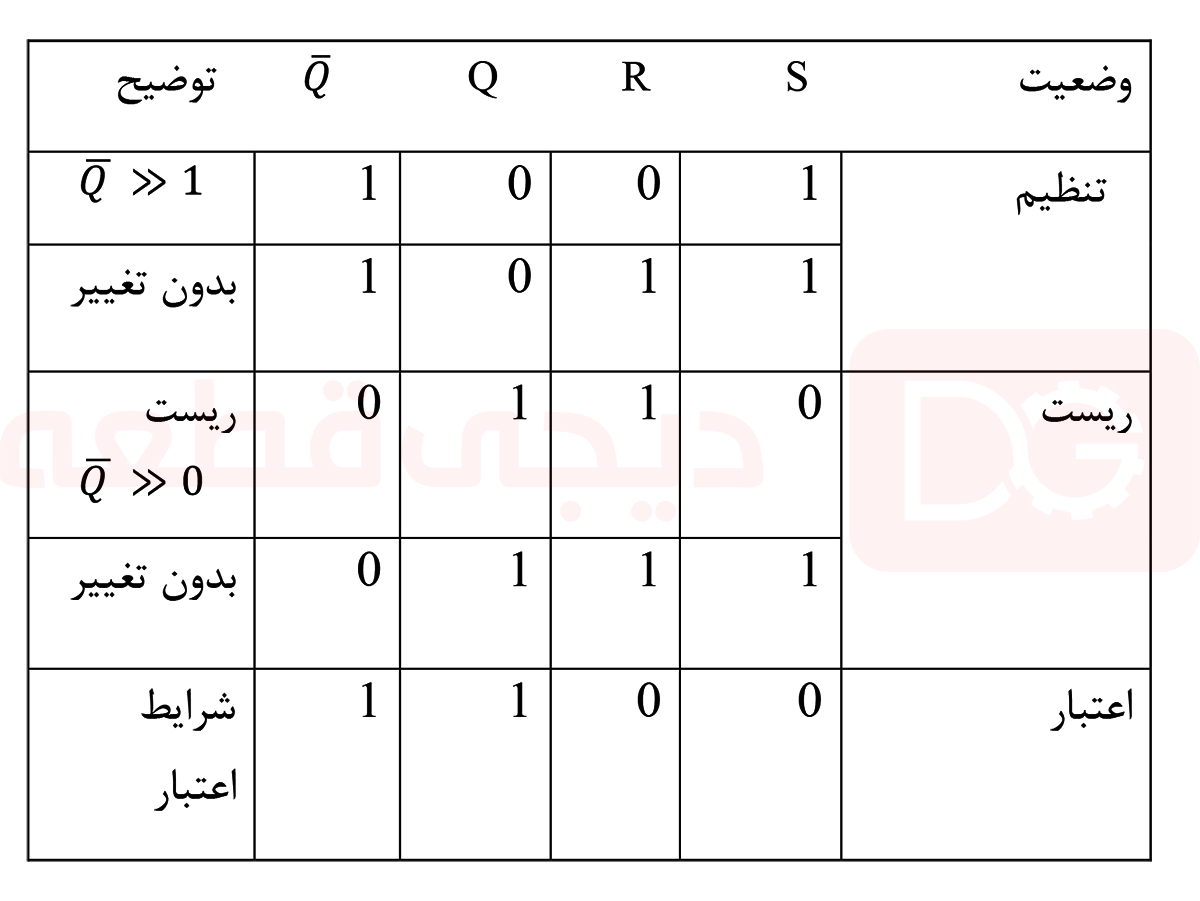

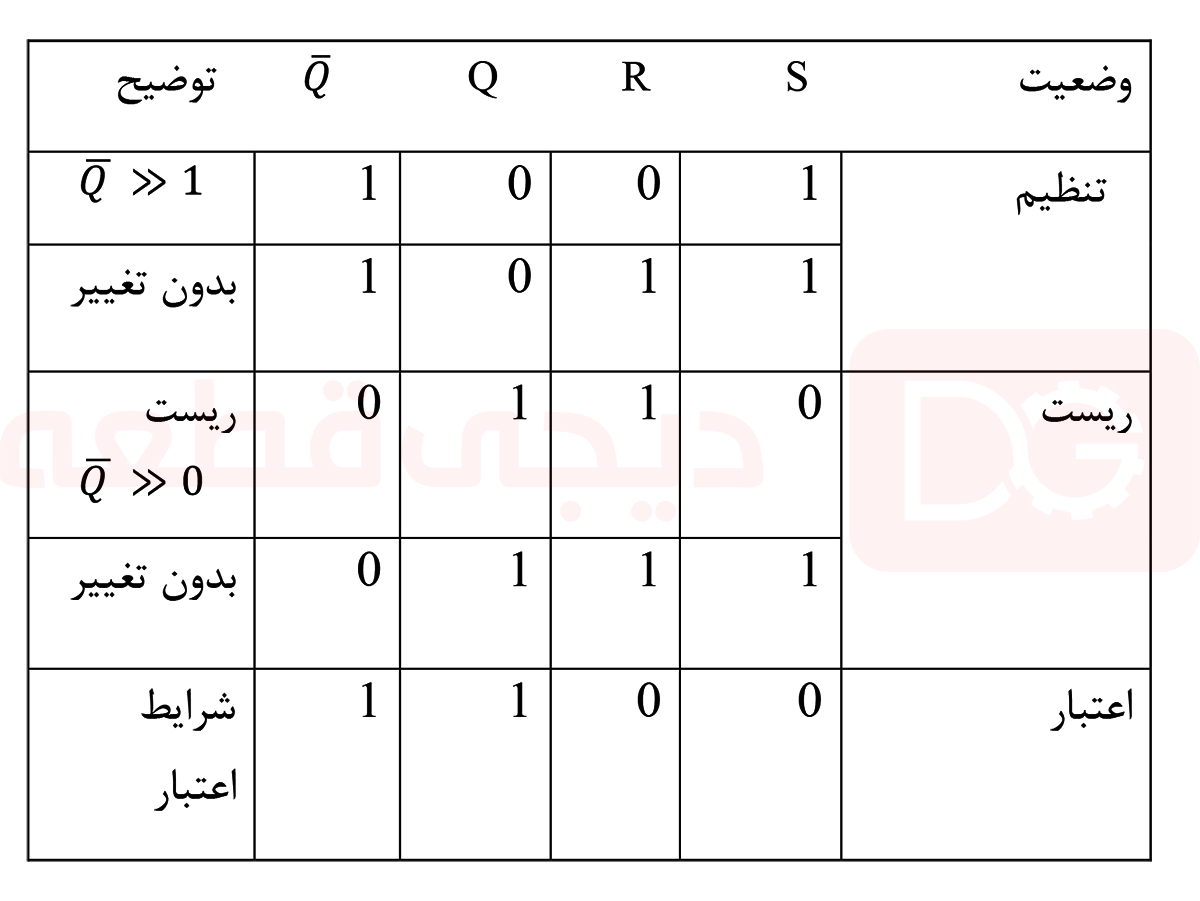

جدول درستی برای این تابع تنظیم-ریست

مشاهده می شود زمانی که هر دو ورودی “S = “1 و “R = “1 هستند وابسته به وضعیت ورودی های S یا R قبل از اینکه این موقعیت وجود داشته باشد، خروجی های Q و میتوانند در هر دو سطح منطقی “1” یا “0” باشند. بنابراین شرایط “S = R = “1” وضعیت خروجی های Q و را تغییر نمیدهد.

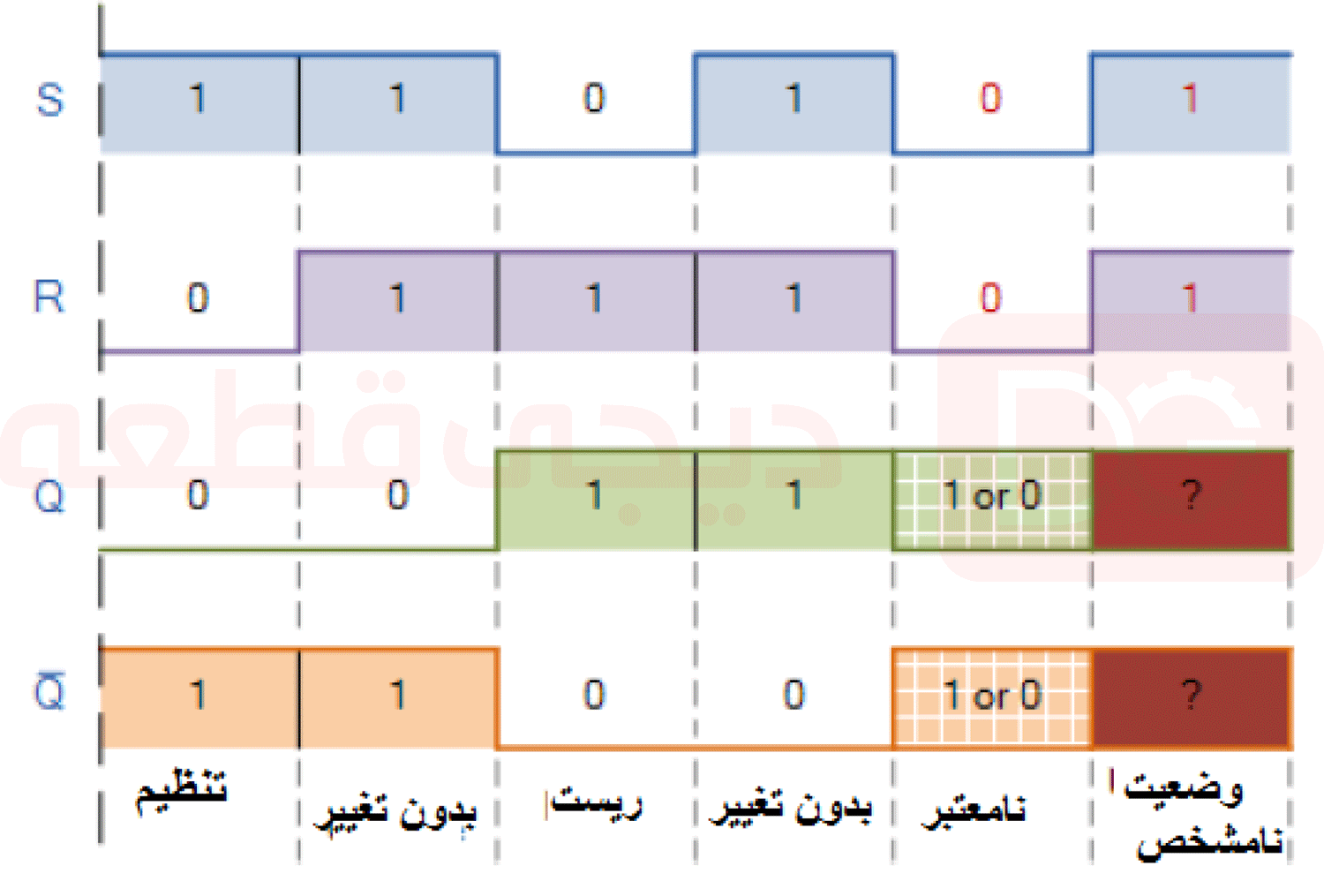

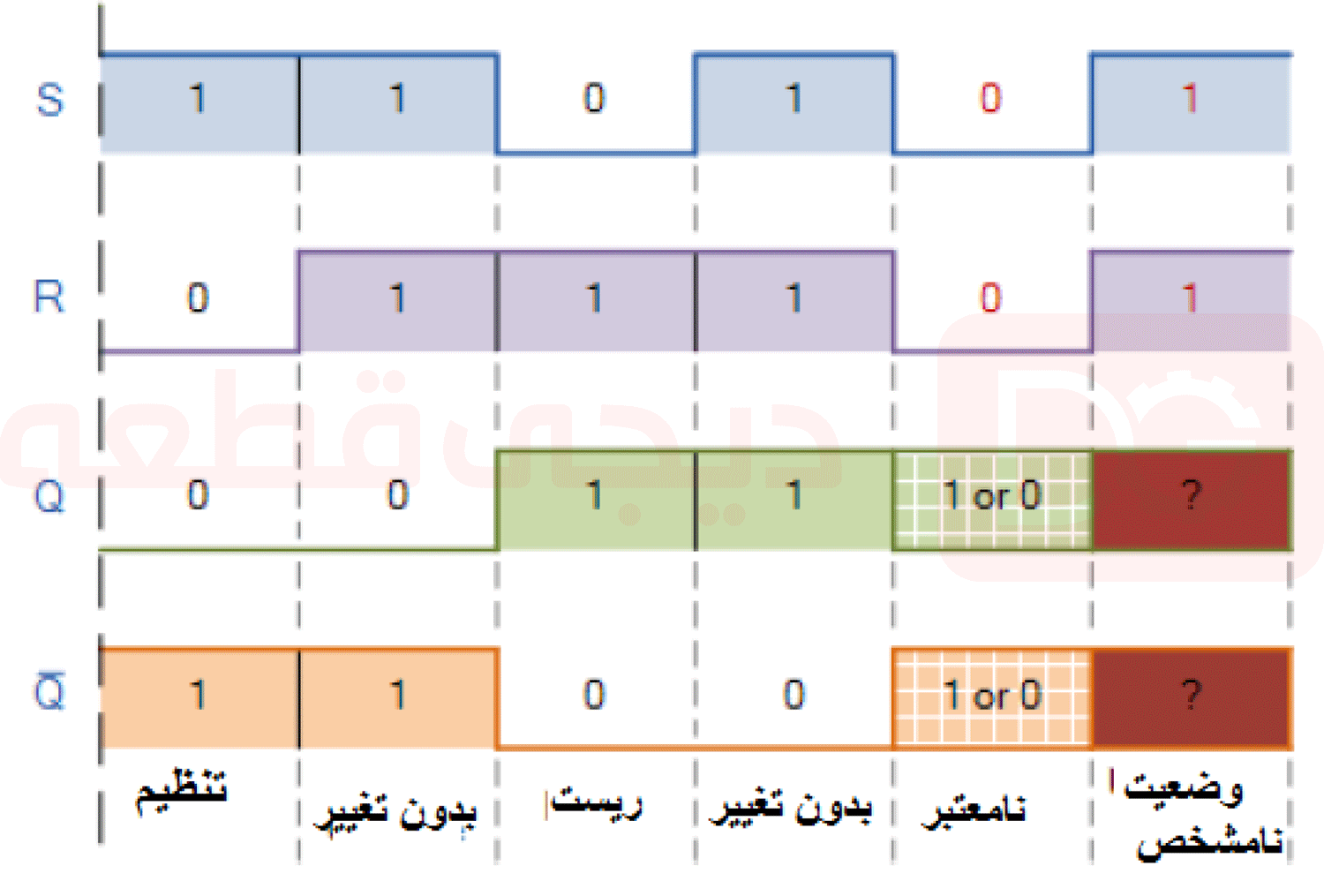

اگرچه، وضعیت ورودی S = “0” و R = “0” یک وضعیت نامطلوب یا نامعتبر است و باید از آن جلوگیری کرد. شرایط” S = R = “0 باعث می شود که هر دو خروجی Q و در سطح منطقی “1” وقتی که معمولاً می خواستیم معکوس Q باشد، با هم بالا باشند. نتیجه این است که فلیپ-فلاپ کنترل Q و را از دست می دهد و اگر دو ورودی پس از این شرط دوباره از “بالا” به منطق “1” برگردند، فلیپ فلاپ ناپایدار می شود و بر اساس عدم تعادل همانطور که در نمودار سوئیچ زیر نشان داده شده است به وضعیت داده نامشخص تبدیل می شود.

دیاگرام سوئیچینگ فلیپ-فلاپ SR

این عدم تعادل می تواند باعث شود که یکی از خروجی ها سریعتر از دیگری تغییر کند و باعث شود که فلیپ فلاپ به یک وضعیت دیگر که ممکن است وضعیت مورد نیاز نباشد تغییر پیدا کند و اختلال داده وجود خواهد داشت. این وضعیت ناپایدار معمولاً به عنوان حالت شبه-پایدار شناخته می شود.

سپس، یک دروازه NAND فلیپ-فلاپ SRیا دروازه NAND قفل SR میتواند با اعمال منطق “0”(پایین) به ورودی تنظیم آن تنظیم شود و با اعمال منطق “0” به ورودی ریست آن دوباره ریست شود. گفته می شود اگر هر دو ورودی تنظیم و ریست به طور همزمان فعال شوند، فلیپ -فلاپ SR در وضعیت “نامعتبر” (شبه-پایدار) قرار میگیرد.

همانطور که در بالا دیدیم، ورودی اصلی دروازه NANDفلیپ-فلاپ SR به ورودی منطقی “0” برای تنظیم یا تغییر وضعیت از Q به و برعکس نیاز دارد. با این وجود می توانیم با استفاده از سیگنال های ورودی مثبت، با اضافه کردن دو دروازه NAND اضافی که به عنوان اینورتر به ورودی های S و R وصل می شوند، مدار فلیپ-فلاپ پایه را تغییر داد.

دروازه NAND مثبت فلیپ-فلاپ SR

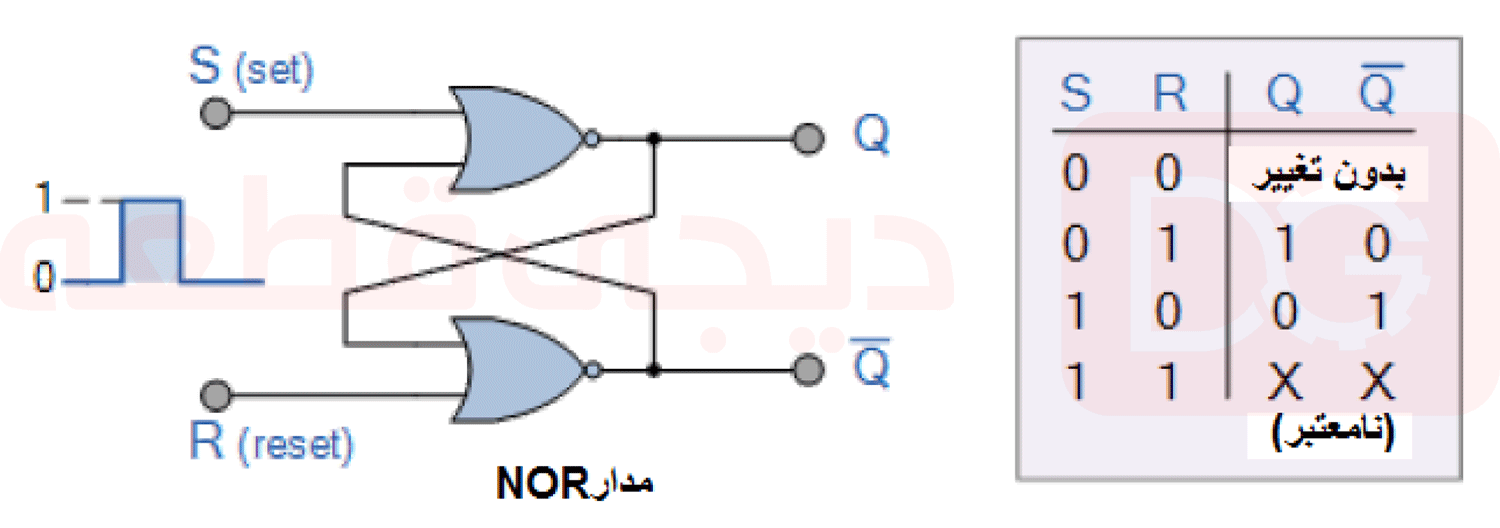

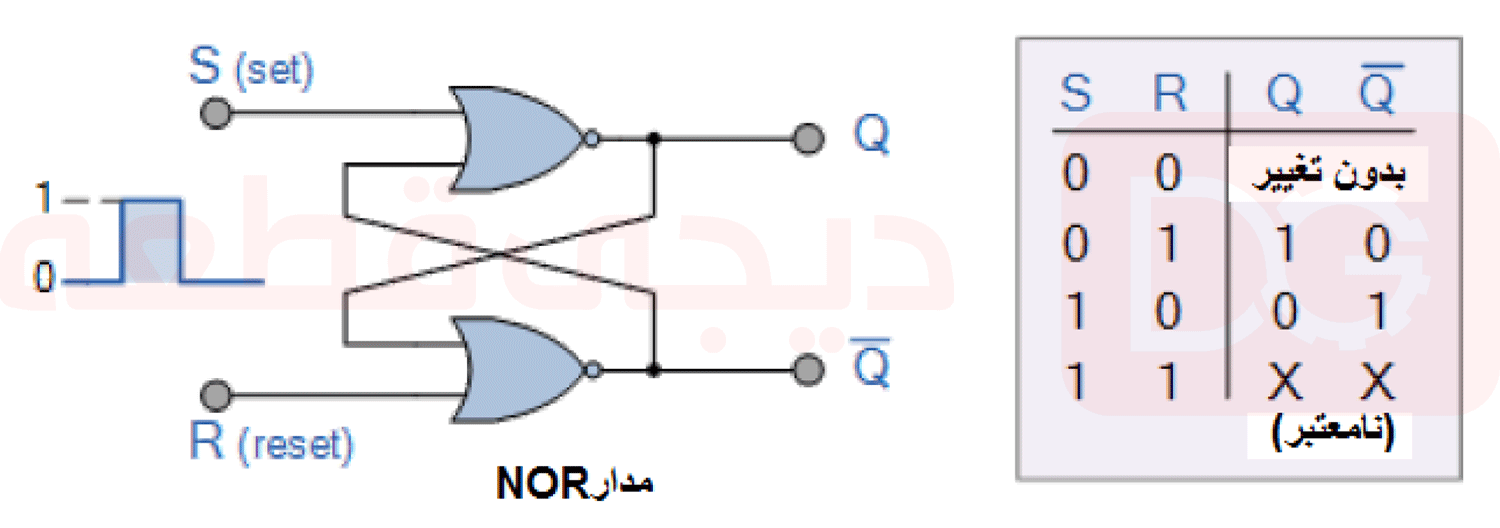

همچنین با استفاده از دروازه های NAND، با استفاده از دو دروازه NOR کوپل-متقاطع که در همان پیکربندی متصل شده اند، می توان فلیپ فلاپ های یک بیتی ساده SR ساخت. مدار به روشی مشابه با مدار دروازه NAND در بالا کار خواهد کرد، به جز اینکه ورودی ها فعال بالا هستند و هنگامی که هر دو ورودی آن در سطح منطقی “1” باشد، وضعیت نامعتبر وجود دارد و این در زیر نشان داده شده است.

دروازه NOR فلیپ-فلاپ SR

مدارهای غیر پرشی سوئیچ

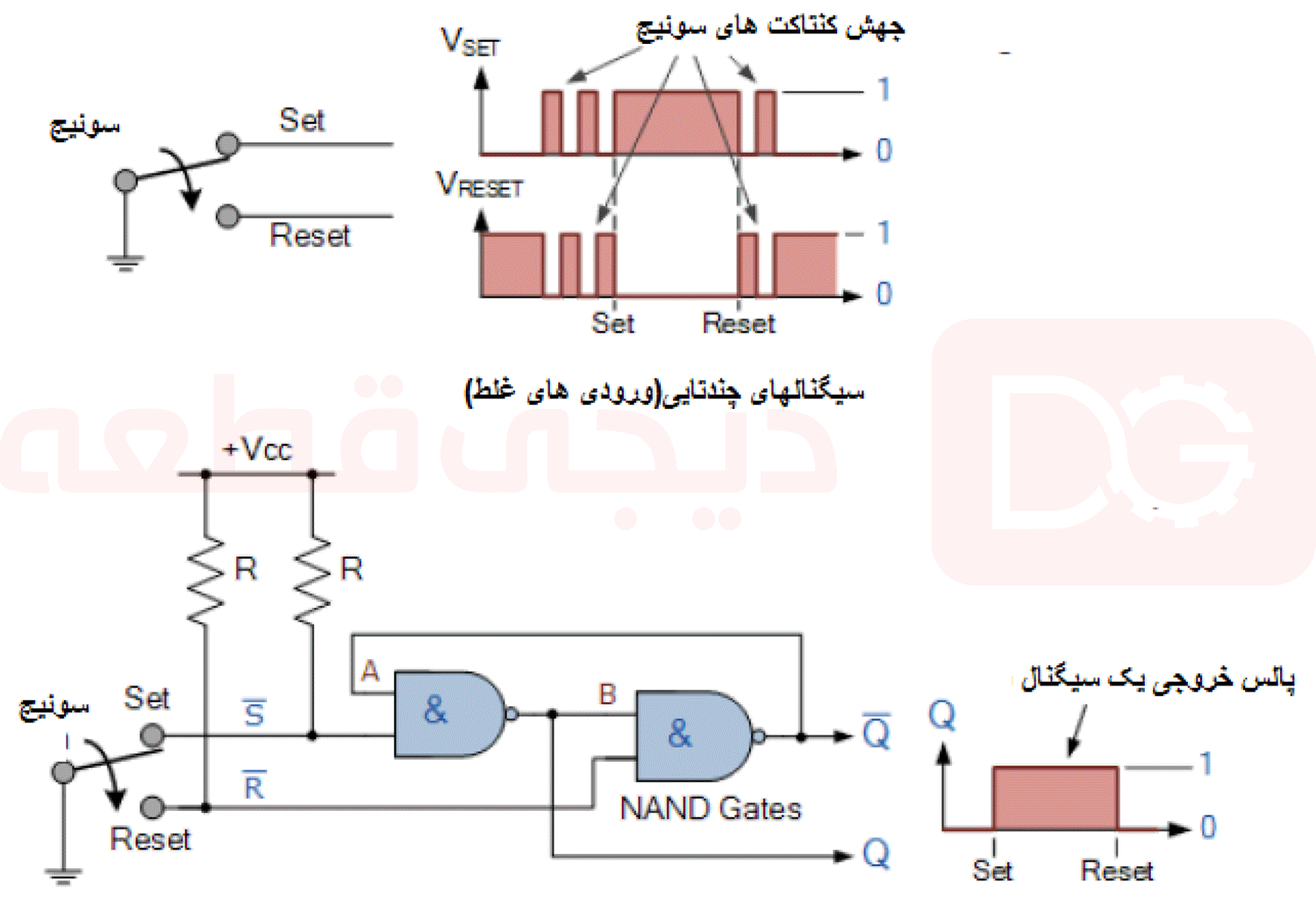

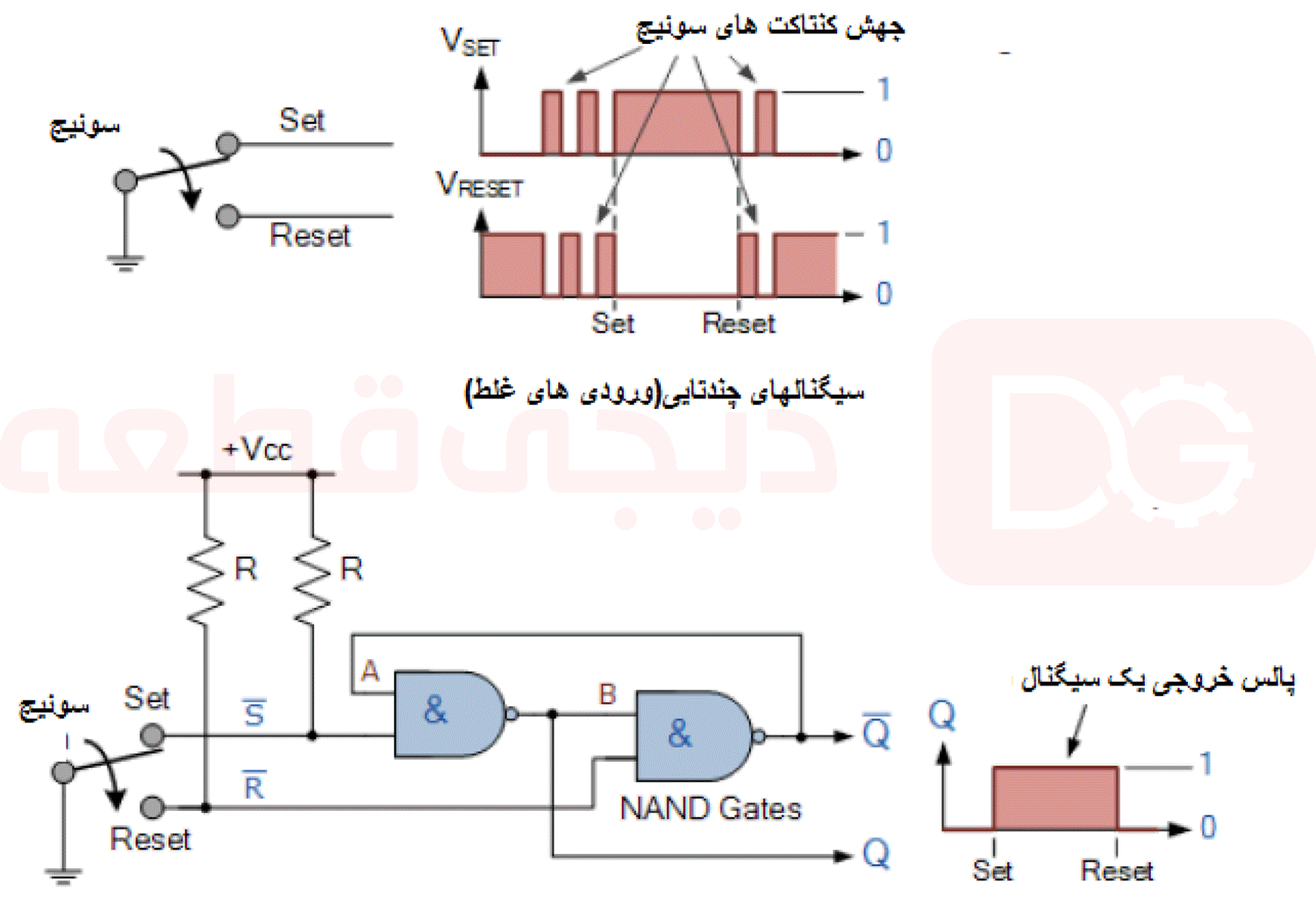

فلیپ-فلاپ های تریگر شده لبه نیاز به انتقال سیگنال با کیفیت دارند و یکی از کاربردهای عملی این نوع مدار های ست-ریست به عنوان قفل است که برای از بین بردن ” پرش” سوئیچ مکانیکی استفاده می شود. همانطور که از نام آن پیداست، پرش سوئیچ هنگامی اتفاق می افتد که هر سوئیچ مکانیکی مانند دکمه فشاری یا صفحه عمل کنند و سوئیچ داخلی کاملاً تمیز بسته نمی شوند، اما ابتدا قبل از بسته شدن (یا باز شدن) هنگام فشار دادن سوئیچ، باهم پرش می کنند .

این امر باعث ایجاد یک سری پالس های منفرد به طول ده ها میلی ثانیه میشود که یک سیستم الکترونیکی یا مدار مانند شمارنده دیجیتال ممکن است به جای یک پالس منفرد طولانی، یک سری از پالس های منطقی را ببیند و غلط رفتار کند. به عنوان مثال، در این دوره جهش ولتاژ خروجی می تواند به طرز شدیدی نوسان کند و ممکن است تعداد ورودی های متعدد را به جای یک عدد واحد ثبت کند. سپس می توان از مدارهای قفل دوپایا یا فلیپ-فلاپ های SR برای از بین بردن این نوع مشکل استفاده کرد و این در زیر نشان داده شده است.

مدار غیر پرشی سوئیچ فلیپ-فلاپ SR

بسته به وضعیت فعلی خروجی، اگر دکمه های ست یا ریست فشرده شوند، خروجی به روشی که در بالا توضیح داده شده تغییر خواهد کرد و هر ورودی اضافی ناخواسته (پرش) از عملکرد مکانیکی سوئیچ، هیچ تاثیری بر روی خروجی Qنخوهد داشت.

هنگامی که دکمه دیگر فشرده می شود، اولین تماس باعث تغییر وضعیت قفل می شود، اما هرگونه فشار اضافی مکانیکی سوئیچ نیز هیچ تاثیری نخواهد داشت. فلیپ- فلاپ SR می تواند پس از مدت زمان کوتاهی، به عنوان مثال 5/0 ثانیه، به صورت خودکار ریست شود به طوری که می تواند هر ورودی تکراری اضافی و تعمدی را از همان تماس های سوئیچ، مانند ورودی های چندتایی از دکمه”بازگشت” ثبت کند.

عموما آی سی هایی که برای رفع مشکل پرش سوئیچ ساخته شده است، عبارتند از MAX6816، ورودی تنها، MAX6817، ورودی دوتایی و آی سی های حذف کننده پرش سوئیچ ورودی MAX6818. این تراشه ها حاوی مدار لازم برای فلیپ فلاپ هستند تا رابطه سوئیچ های مکانیکی به سیستم های دیجیتالی را فراهم کنند.

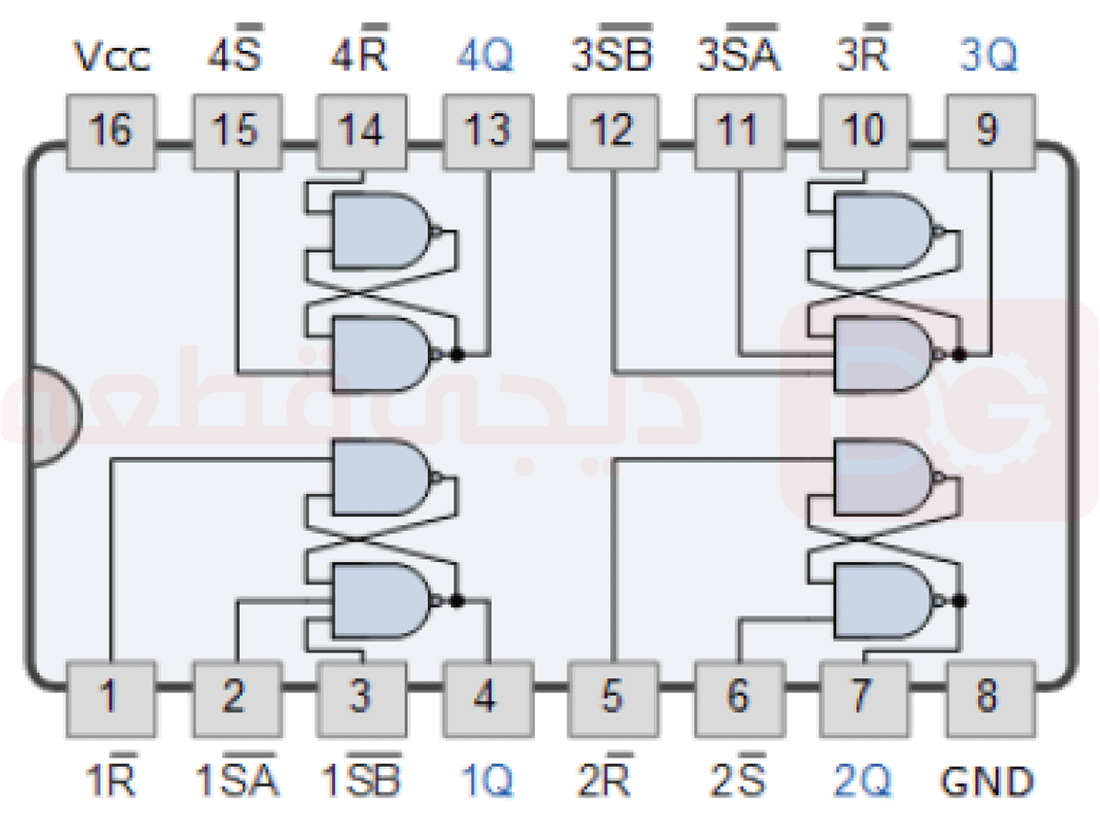

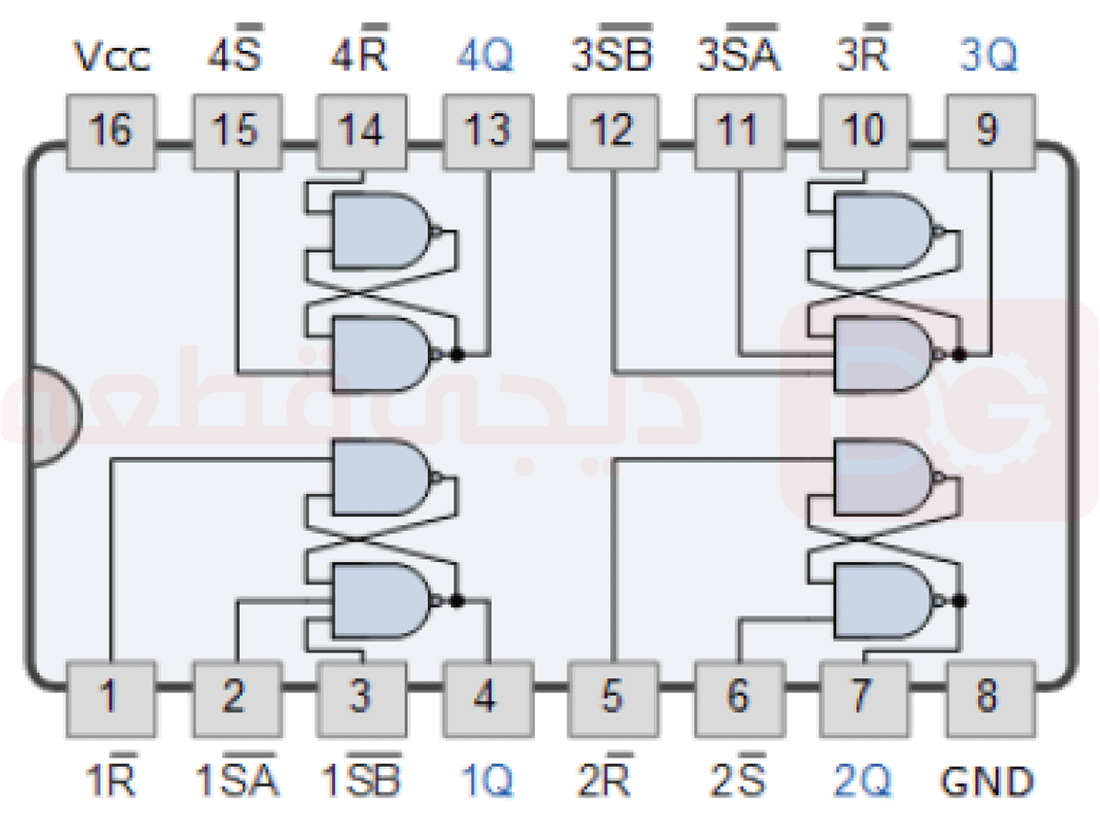

قفل های دوپایا ست-ریست می توانند به عنوان ژنراتور های پالس مونواستابل(یک -شات) برای تولید یک پالس خروجی منفرد یا بالا یا پایین از برخی پهنای یا مدت زمان مشخص برای زمان بندی یا اهداف کنترل بکارروند. 74LS279 یک ای سی قفل دوپایا SR چهارگوش است که شامل چهار نوع NAND دوپایا در یک تراشه است که امکان حذف پرش سوئیچ یا مدارهای ساعت پایدار / مونواستابل را دارد و به راحتی ساخته می شوند.

قفل دوپایا SR چهار گوش 74LS279

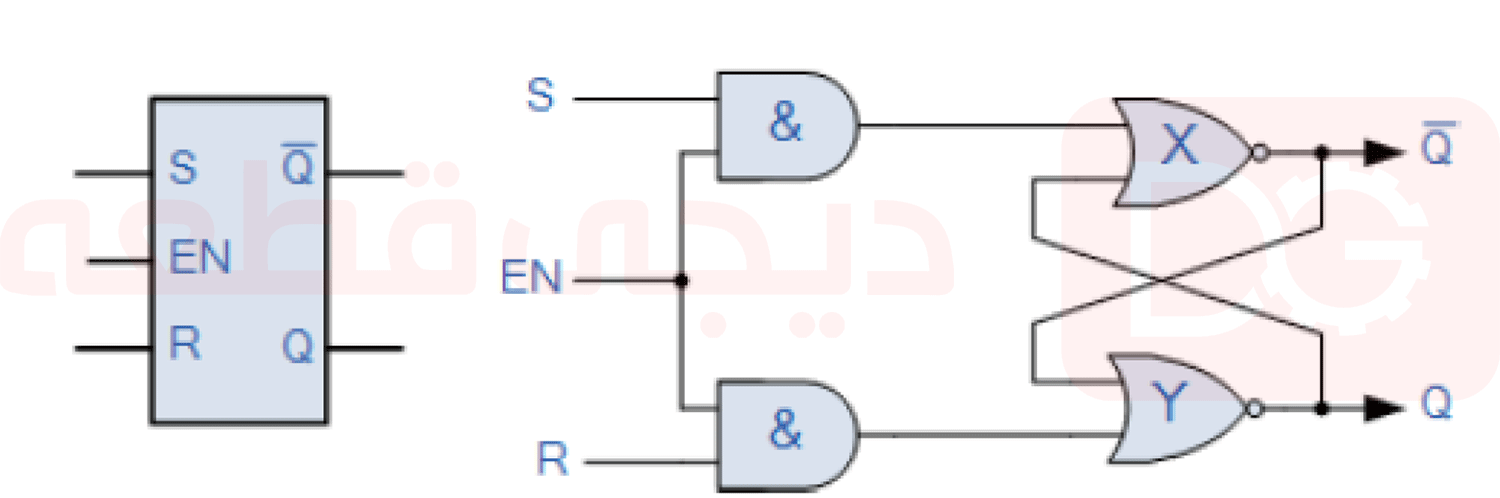

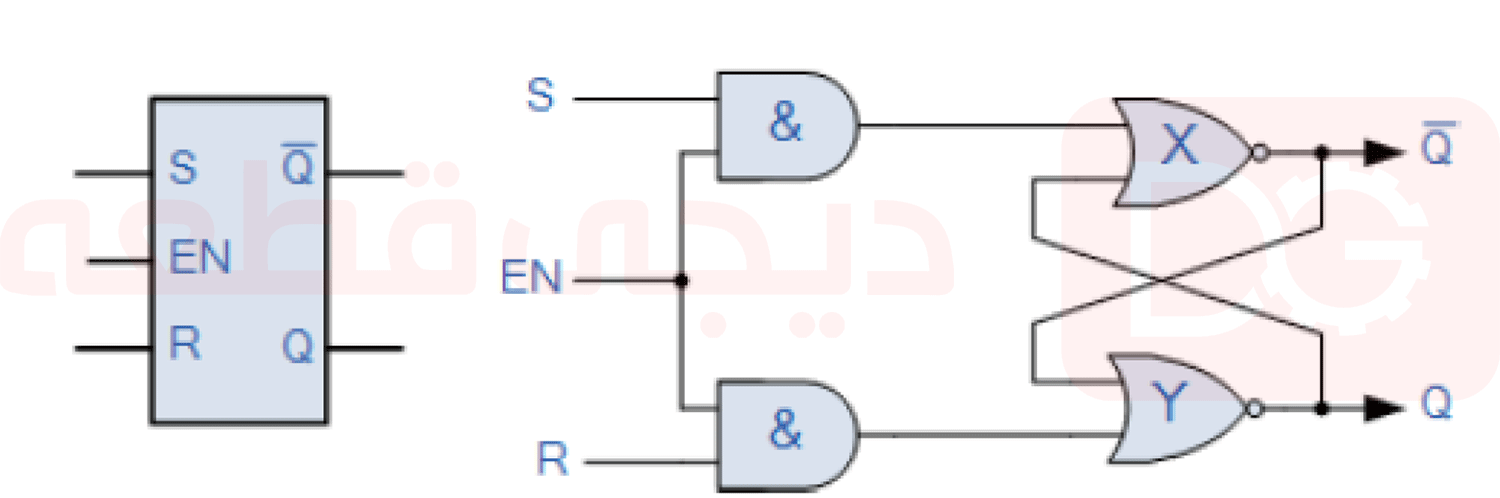

فلیپ-فلاپ SR ساعت یا گیت دار

در مدارهای منطقی متوالی بعضی اوقات مطلوب است که یک فلیپ فلاپ SR قابل قبول داشته باشیم که تنها در شرایط خاصی بدون در نظر گرفتن شرایط ورودی یا ریست برآورده شود، حالت تغییر می کند. با اتصال یک دروازه 2 -ورودی AND در توالی با هر ترمینال ورودی فلیپ-فلاپ SR، یک فلیپ-فلاپ SR گیت دار میتوان ایجاد کرد.

این ورودی شرطی اضافی یک ورودی “فعال” نامیده میشود و پیشوند “EN” را میدهد. علاوه بر این ورودی بدان معنی است که خروجی در Q فقط در حالت بالا وضعیت را تغییر می دهد و بنابراین می تواند به عنوان ورودی ساعت (CLK) مورد استفاده قرار گیرد و آن را حساس به سطح کند که در زیر نشان داده شده است.

فلیپ-فلاپ SR گیت دار

زمانی که ورودی “EN” در سطح منطقی “0” باشد، خروجی های دو دروازه AND نیز در سطح منطقی “0” ، (اصول دروازه AND) بدون در نظر گرفتن شرایط دو ورودی S و R، دو خروجی Q و را به آخرین وضعیت معلوم خود تبدیل می کنند. هنگامی که ورودی فعال “EN” به سطح منطق “1” تغییر میکند، مدار به عنوان یک فلیپ فلاپ دوپایاSR با دو دروازه AND و با شفافیت نسبت به سیگنال های ست و ریست پاسخ میدهد.

این ورودی فعال اضافی همچنین می تواند به یک سیگنال زمان بندی ساعت (CLK) متصل شود و همزمان سازی ساعت را در فلاپ فلاپ ایجاد کند چیزی که گاهی اوقات”فلیپ-فلاپ SR ” نامیده می شود. بنابراین یک فلیپ-فلاپ SR دوپایا گیت دار به عنوان یک قفل دوپایا استاندارد عمل می کند، اما خروجی ها فقط هنگامی فعال می شوند که یک منطق “1” به ورودی EN آن اعمال شود و با یک منطق “0” غیرفعال شود.

در آموزش بعدی درمورد مدارهای منطقی متوالی، بر نوع دیگری از فلیپ-فلاپ با لبه ساده خواهیم پرداخت که بسیار شبیه فلیپ –فلاپ SR با نام فلیپ-فلاپ JKبه نام مخترع خود یعنی Jack Kilby است. این قطعه از پرکاربردترین ها در تمام طراحی های فلیپ فلاپ است زیرا به عنوان یک قطعه جهانی در نظر گرفته می شود.